|

|

PDF ADAU1961 Data sheet ( Hoja de datos )

| Número de pieza | ADAU1961 | |

| Descripción | 24-Bit Audio Codec | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADAU1961 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

Stereo, Low Power, 96 kHz, 24-Bit

Audio Codec with Integrated PLL

ADAU1961

FEATURES

GENERAL DESCRIPTION

24-bit stereo audio ADC and DAC: >98 dB SNR

Sampling rates from 8 kHz to 96 kHz

Low power: 17 mW record, 18 mW playback, 48 kHz

6 analog input pins, configurable for single-ended or

differential inputs

Flexible analog input/output mixers

Stereo digital microphone input

Analog outputs: 2 differential stereo, 2 single-ended stereo,

1 mono headphone output driver

PLL supporting input clocks from 8 MHz to 27 MHz

Analog automatic level control (ALC)

Microphone bias reference voltage

Analog and digital I/O: 3.3 V

I2C and SPI control interfaces

Digital audio serial data I/O: stereo and time-division

multiplexing (TDM) modes

Software-controllable clickless mute

32-lead, 5 mm × 5 mm LFCSP

−40°C to +105°C operating temperature range

Qualified for automotive applications

APPLICATIONS

The ADAU1961 is a low power, stereo audio codec that supports

stereo 48 kHz record and playback at 35 mW from a 3.3 V analog

supply. The stereo audio ADCs and DACs support sample rates

from 8 kHz to 96 kHz as well as a digital volume control.

The record path includes an integrated microphone bias circuit

and six inputs. The inputs can be mixed and muxed before the

ADC, or they can be configured to bypass the ADC. The

ADAU1961 includes a stereo digital microphone input.

The ADAU1961 includes five high power output drivers (two

differential and three single-ended), supporting stereo head-

phones, an earpiece, or other output transducer. AC-coupled

or capless configurations are supported. Individual fine level

controls are supported on all analog outputs. The output mixer

stage allows for flexible routing of audio.

The serial control bus supports the I2C and SPI protocols. The

serial audio bus is programmable for I2S, left-/right-justified,

and TDM modes. A programmable PLL supports flexible clock

generation for all standard integer rates and fractional master

clocks from 8 MHz to 27 MHz.

Automotive head units

Automotive amplifiers

Navigation systems

Rear-seat entertainment systems

FUNCTIONAL BLOCK DIAGRAM

JACKDET/MICIN

HP JACK REGULATOR

DETECTION

ADAU1961

LAUX

LINP

LINN

RINP

RINN

RAUX

INPUT

MIXERS

ALC

ADC

ADC

ADC

DAC

DIGITAL DIGITAL

FILTERS FILTERS

DAC

DAC

OUTPUT

MIXERS

LOUTP

LOUTN

LHP

MONOOUT

RHP

ROUTP

ROUTN

MICBIAS

MICROPHONE

BIAS

PLL

SERIAL DATA

INPUT/OUTPUT PORTS

I2C/SPI

CONTROL PORT

MCLK ADC_SDATA

DAC_SDATA ADDR0/ ADDR1/ SCL/ SDA/

CLATCH CDATA CCLK COUT

Figure 1.

Rev. A

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibilityisassumedbyAnalogDevices for itsuse,nor foranyinfringementsofpatentsor other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2010–2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

1 page

ADAU1961

Parameter

Mute Attenuation

Interchannel Gain Mismatch

Offset Error

Gain Error

Interchannel Isolation

Common-Mode Rejection Ratio

FULL DIFFERENTIAL PGA INPUT

Full-Scale Input Voltage (0 dB)

Dynamic Range

With A-Weighted Filter (RMS)

No Filter (RMS)

Total Harmonic Distortion + Noise

Signal-to-Noise Ratio

With A-Weighted Filter (RMS)

No Filter (RMS)

PGA Boost Gain Error

Mute Attenuation

Interchannel Gain Mismatch

Offset Error

Gain Error

Interchannel Isolation

Common-Mode Rejection Ratio

MICROPHONE BIAS

Bias Voltage

0.65 × AVDD

0.90 × AVDD

Bias Current Source

Noise in the Signal Bandwidth

DIGITAL-TO-ANALOG CONVERTERS

DAC Resolution

Digital Attenuation Step

Digital Attenuation Range

DAC TO LINE OUTPUT

Full-Scale Output Voltage (0 dB)

Dynamic Range

With A-Weighted Filter (RMS)

No Filter (RMS)

Test Conditions/Comments

PGA muted

LDMUTE, RDMUTE = 0

RDBOOST[1:0], LDBOOST[1:0] = 00

100 mV rms, 1 kHz

100 mV rms, 20 kHz

Differential PGA inputs

20 Hz to 20 kHz, −60 dB input

−1 dBFS

Min

−0.6

−6

−24

−52

94

91

20 dB gain setting (RDBOOST[1:0],

LDBOOST[1:0] = 10)

PGA muted

LDMUTE, RDMUTE = 0

RDBOOST[1:0], LDBOOST[1:0] = 00

−8

−0.3

−6

−17

100 mV rms, 1 kHz

100 mV rms, 20 kHz

MBIEN = 1

−52

MBI = 1, MPERF = 0

MBI = 1, MPERF = 1

MBI = 0, MPERF = 0

MBI = 0, MPERF = 1

MBI = 0, MPERF = 1

1 kHz to 20 kHz

MBI = 0, MPERF = 0

MBI = 0, MPERF = 1

MBI = 1, MPERF = 0

MBI = 1, MPERF = 1

DAC performance excludes mixers and

headphone amplifier

All DACs

2.00

2.04

2.89

2.89

13

20 Hz to 20 kHz, −60 dBFS input, line

output mode

95

93.5

Rev. A | Page 4 of 76

Data Sheet

Typ

−76

−87

−0.073

0

−14

83

−58

−48

1.0 (2.83)

98

95

−78

98

95

−0.15

Max

−73

−82

+0.6

+6

−3

−44

−74

+8

Unit

dB

dB

dB

mV

%

dB

dB

dB

V rms (V p-p)

dB

dB

dB

dB

dB

dB

−76

−87

−0.0005

0

−14

83

−58

−48

−73

−82

+0.3

+6

−9

−44

dB

dB

dB

mV

%

dB

dB

dB

2.145

2.13

2.97

2.99

42

85

25

22

2.19

2.21

3.04

3.11

3

36

V

V

V

V

mA

nV/√Hz

nV/√Hz

nV/√Hz

nV/√Hz

24

0.375

95

0.92 (2.60)

101

98

Bits

dB

dB

V rms (V p-p)

dB

dB

5 Page

ADAU1961

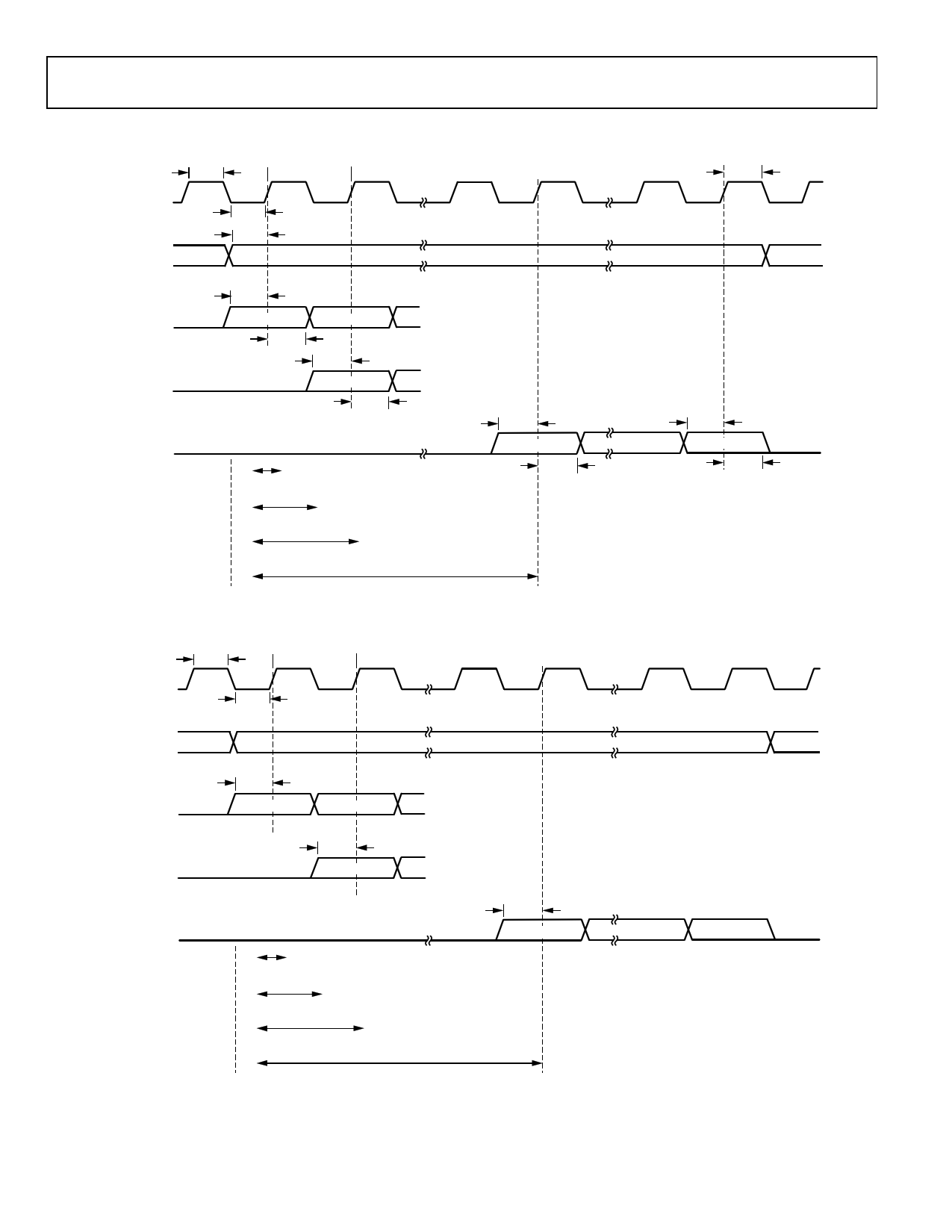

DIGITAL TIMING DIAGRAMS

BCLK

LRCLK

tBIH

tBIL

tLIS

DAC_SDATA

LEFT-JUSTIFIED

MODE

DAC_SDATA

I2S MODE

DAC_SDATA

RIGHT-JUSTIFIED

MODE

tSIS

MSB

tSIH

MSB – 1

tSIS

MSB

tSIH

8-BIT CLOCKS

(24-BIT DATA)

tSIS

MSB

tSIH

12-BIT CLOCKS

(20-BIT DATA)

14-BIT CLOCKS

(18-BIT DATA)

16-BIT CLOCKS

(16-BIT DATA)

Figure 2. Serial Input Port Timing

BCLK

tBIH

tBIL

LRCLK

ADC_SDATA

LEFT-JUSTIFIED

MODE

ADC_SDATA

I2S MODE

ADC_SDATA

RIGHT-JUSTIFIED

MODE

tSODM

MSB

MSB – 1

tSODM

MSB

8-BIT CLOCKS

(24-BIT DATA)

12-BIT CLOCKS

(20-BIT DATA)

14-BIT CLOCKS

(18-BIT DATA)

16-BIT CLOCKS

(16-BIT DATA)

tSODM

MSB

Figure 3. Serial Output Port Timing

Rev. A | Page 10 of 76

Data Sheet

tLIH

tSIS

LSB

tSIH

LSB

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ADAU1961.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADAU1961 | 24-Bit Audio Codec | Analog Devices |

| ADAU1962 | 24-Bit DAC | Analog Devices |

| ADAU1962A | 24-Bit DAC | Analog Devices |

| ADAU1966 | 16-Channel High Performance | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |