|

|

PDF EDBA232B1MA Data sheet ( Hoja de datos )

| Número de pieza | EDBA232B1MA | |

| Descripción | 16G bits DDR2 Mobile RAM | |

| Fabricantes | Elpida Memory | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EDBA232B1MA (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

DATA SHEET

16G bits DDR2 Mobile RAM™, QDP

EDBA232B1MA (512M words × 32 bits)

Specifications

• Density: 16G bits

• Organization

— 32M words × 32 bits × 8 banks × 2 ranks

— 4 pieces of 4Gb (×16) in one package

• Data rate: 1066Mbps (max.)

• Package

— 134-ball FBGA, QDP (Quad Die Package)

— Package size: 11.5mm × 13.0mm

— Ball pitch: 0.65mm

— Lead-free (RoHS compliant) and Halogen-free

• Power supply

— VDD1 = 1.70V to 1.95V

— VDD2, VDDQ = 1.14V to 1.30V

• Interface: HSUL_12

• Operating case temperature range

— TC = -30°C to +85°C

Features

• JEDEC LPDDR2-S4B compliance

• DLL is not implemented

• Low power consumption

• Mobile RAM functions

— Partial Array Self-Refresh (PASR)

— Auto Temperature Compensated Self-Refresh

(ATCSR) by built-in temperature sensor

— Deep power-down mode

— Per Bank Refresh

Block Diagram

CKE0 /CS0

CKE1 /CS1

CK, /CK

CA0 to CA9

VDD1

VDD2

VDDQ

VREFCA

VREFDQ

VSS

4G bits

(256M x 16)

4G bits

(256M x 16)

4G bits

(256M x 16)

4G bits

(256M x 16)

DQS0, /DQS0

DQS1, /DQS1

DQ0 to DQ15

DM0, DM1

ZQ0

DQS2, /DQS2

DQS3, /DQS3

DQ16 to DQ31

DM2, DM3

ZQ1

Document No. E1784E30 (Ver. 3.0)

Date Published March 2012 (K) Japan

Printed in Japan

URL: http://www.elpida.com

Elpida Memory, Inc. 2011-2012

1 page

EDBA232B1MA

Pin Descriptions

Pin name

Function

CK, /CK

Clock

CKE0, CKE1

Clock enable

/CS0, /CS1

Chip select

CA0 to CA9

DDR command/address inputs

(Address configurations: Row:R0-R13,

Column:C0-C10,

Bank:BA0-BA2)

DM0 to DM3

Input data mask

DQ0 to DQ31

Data input/output

DQS0 to DQS3

/DQS0 to /DQS3

Data strobe

VDD1

VDD2*1

VDDQ*1

Core power supply 1

Core power supply 2 and input receiver power supply

I/O power supply

VREFCA

Reference voltage for CA input receiver

VREFDQ

Reference voltage for DQ input receiver

VSS

Ground

ZQ

NC*2

NU*3

Reference pin for output drive strength calibration

No connection

Not usable

Notes: 1. VDD2 and VDDQ are merged on the package substrate.

2. Not internally connected.

3. Don’t connect. Internally connected.

Data Sheet E1784E30 (Ver. 3.0)

5

5 Page

EDBA232B1MA

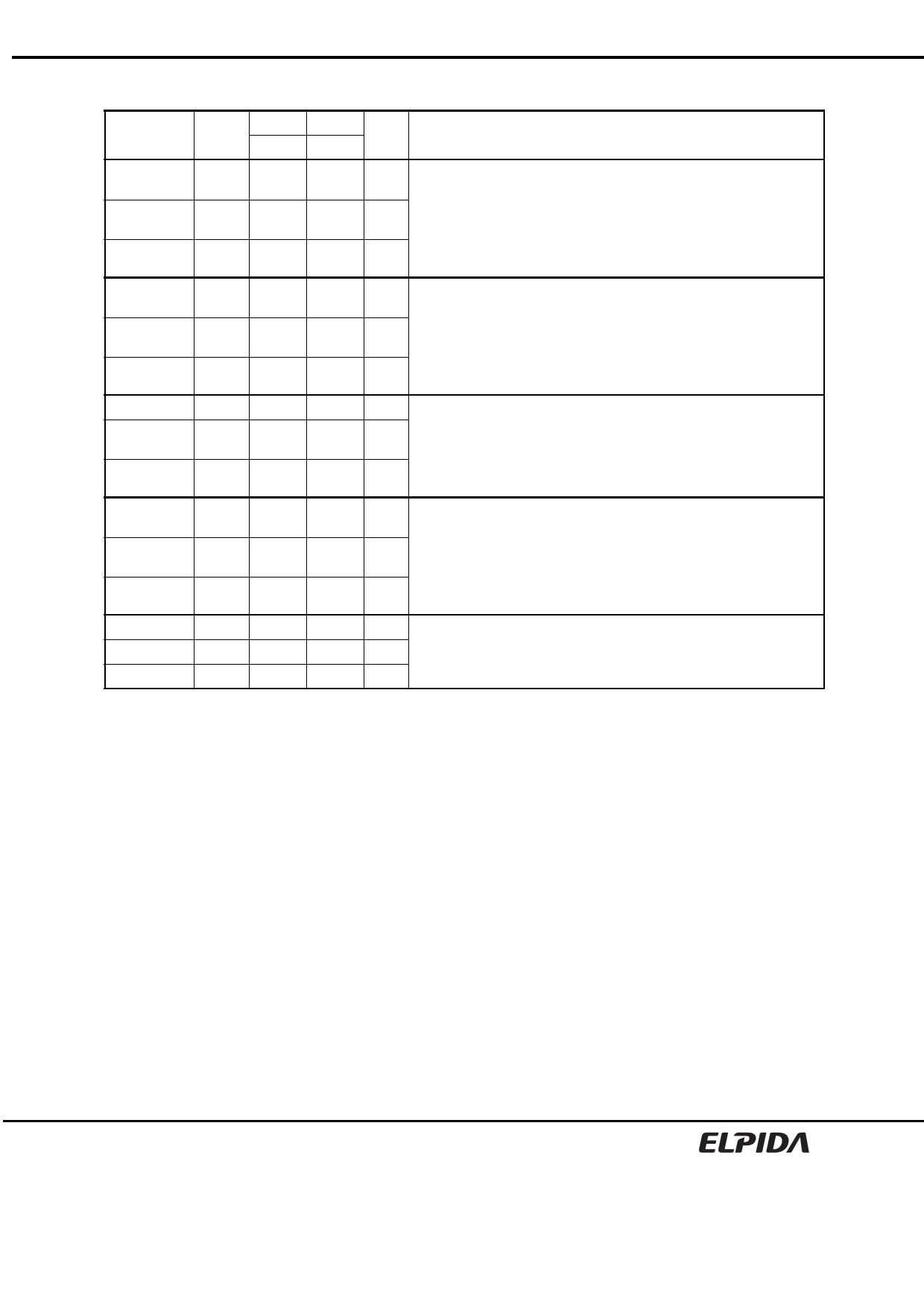

Table 3 IDD Specification Parameters and Operating Conditions (cont’d)

Symbol

Power

Supply

1066

max.

800 Unit

max.

Parameter/Condition

IDD4W_1

VDD1

4.0

4.0 mA 2 pieces of devices in operating burst write

The other in deep power down

Conditions for operating devices are:

IDD4W_2 VDD2 380 310 mA tCK = tCK(avg)min; /CS is HIGH between valid commands;

One bank active; BL = 4; WL = WLmin;

IDD4W_IN VDDQ

2.0

2.0 mA

CA bus inputs are SWITCHING;

50% data change each burst transfer;

IDD5_1

IDD5_2

IDD5_IN

VDD1

80

80 mA 2 pieces of devices in all bank auto-refresh

The other in deep power down

Conditions for operating devices are:

VDD2 300 300 mA tCK = tCK(avg)min; CKE is HIGH between valid commands;

tRC = tRFCabmin; Burst refresh;

VDDQ

2.0

2.0 mA CA bus inputs are SWITCHING;

Data bus inputs are STABLE;

IDD5AB_1

IDD5AB_2

VDD1

VDD2

IDD5AB_IN VDDQ

4.0

32

2.0

4.0 mA

30 mA

2.0 mA

2 pieces of devices in all bank auto-refresh

The other in deep power down

Conditions for operating devices are:

tCK = tCK(avg)min; CKE is HIGH between valid commands; tRC = tREFI;

CA bus inputs are SWITCHING;

Data bus inputs are STABLE;

IDD5PB_1 VDD1

IDD5PB_2 VDD2

IDD5PB_IN VDDQ

4.0

32

2.0

4.0 mA

30 mA

2.0 mA

2 pieces of devices in per bank auto-refresh

The other in deep power down

Conditions for operating devices are:

tCK = tCK(avg)min; CKE is HIGH between valid commands;

tRC = tREFI/8;

CA bus inputs are SWITCHING;

Data bus inputs are STABLE;

IDD8_1

IDD8_2

IDD8_IN

VDD1

VDD2

VDDQ

64

24

48

64 µA

24 µA

48 µA

All devices in deep power-down

CK = LOW, /CK = HIGH; CKE is LOW;

CA bus inputs are STABLE;

Data bus inputs are STABLE;

Notes: 1. IDD values published are the maximum of the distribution of the arithmetic mean.

2. IDD current specifications are tested after the device is properly initialized.

Data Sheet E1784E30 (Ver. 3.0)

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet EDBA232B1MA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EDBA232B1MA | 16G bits DDR2 Mobile RAM | Elpida Memory |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |