|

|

PDF AD9644 Data sheet ( Hoja de datos )

| Número de pieza | AD9644 | |

| Descripción | 1.8V Dual Serial Output Analog-to-Digital Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9644 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

14-Bit, 80 MSPS/155 MSPS, 1.8 V Dual

Serial Output Analog-to-Digital Converter (ADC)

AD9644

FEATURES

JESD204A coded serial digital outputs

SNR = 73.7 dBFS at 70 MHz and 80 MSPS

SNR = 71.7 dBFS at 70 MHz and 155 MSPS

SFDR = 92 dBc at 70 MHz and 80 MSPS

SFDR = 92 dBc at 70 MHz and 155 MSPS

Low power: 423 mW at 80 MSPS, 567 mW at 155 MSPS

1.8 V supply operation

Integer 1-to-8 input clock divider

IF sampling frequencies to 250 MHz

−148.6 dBFS/Hz input noise at 180 MHz and 80 MSPS

−150.3 dBFS/Hz input noise at 180 MHz and 155 MSPS

Programmable internal ADC voltage reference

Flexible analog input range: 1.4 V p-p to 2.1 V p-p

ADC clock duty cycle stabilizer

Serial port control

User-configurable, built-in self-test (BIST) capability

Energy-saving power-down modes

APPLICATIONS

Communications

Diversity radio systems

Multimode digital receivers (3G and 4G)

GSM, EDGE, W-CDMA, LTE,

CDMA2000, WiMAX, TD-SCDMA

I/Q demodulation systems

Smart antenna systems

General-purpose software radios

Broadband data applications

Ultrasound equipment

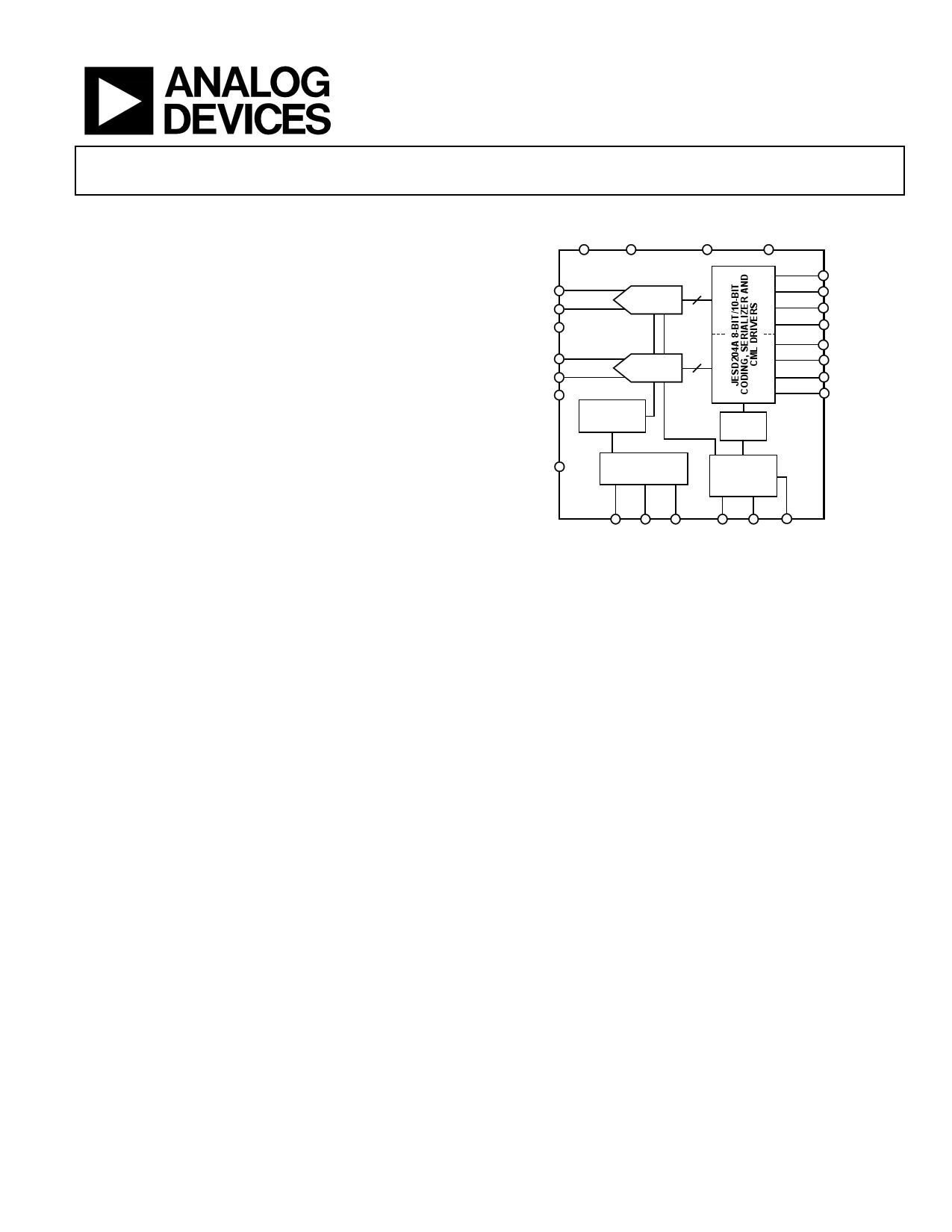

FUNCTIONAL BLOCK DIAGRAM

AVDD AGND

DRVDD

DRGND

VIN+A

VIN–A

VCMA

VIN+B

VIN–B

VCMB

AD9644

PIPELINE

14-BIT ADC

14

PIPELINE 14

14-BIT ADC

REFERENCE

PLL

DOUT+A

DOUT–A

DSYNC+A

DSYNC–A

DOUT+B

DOUT–B

DSYNC+B

DSYNC–B

PDWN

SERIAL PORT

(SPI)

1 TO 8

CLOCK

DIVIDER

SCLK SDIO CSB

CLK+ CLK– SYNC

Figure 1. 48-Lead 7 mm × 7 mm LFCSP

PRODUCT HIGHLIGHTS

1. An on-chip PLL allows users to provide a single ADC

sampling clock; the PLL multiplies the ADC sampling

clock to produce the corresponding JESD204A data rate

clock.

2. The configurable JESD204A output block supports up to

1.6 Gbps per channel data rate when using a dedicated

data link per ADC or 3.2 Gbps data rate when using a

single shared data link for both ADCs.

3. Proprietary differential input that maintains excellent SNR

performance for input frequencies up to 250 MHz.

4. Operation from a single 1.8 V power supply.

5. Standard serial port interface (SPI) that supports various

product features and functions, such as data formatting

(offset binary, twos complement, or gray coding),

controlling the clock DCS, power-down, test modes,

voltage reference mode, and serial output configuration.

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113 ©2010–2012 Analog Devices, Inc. All rights reserved.

1 page

AD9644

Data Sheet

SPECIFICATIONS

ADC DC SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, maximum sample rate, 1.75 V p-p differential input, VIN = −1.0 dBFS differential input, DCS enabled,

unless otherwise noted.

Table 1.

Parameter

RESOLUTION

ACCURACY

No Missing Codes

Offset Error

Gain Error

Differential Nonlinearity (DNL)1

Integral Nonlinearity (INL)1

MATCHING CHARACTERISTIC

Offset Error

Gain Error

TEMPERATURE DRIFT

Offset Error

Gain Error

INPUT REFERRED NOISE

ANALOG INPUT

Input Span

Input Capacitance2

Input Resistance

VCM OUTPUT LEVEL

POWER SUPPLIES

Supply Voltage

AVDD

DRVDD

Supply Current

IAVDD1

IDRVDD1

POWER CONSUMPTION

Sine Wave Input1

Standby Power3

Power-Down Power

Temperature Min

Full 14

AD9644-80

Typ Max

Full Guaranteed

Full ±2 ±10

Full

−7 −2.5

+1

Full ±0.55

25°C ±0.3

Full ±1.1

25°C ±0.5

Full

−7 +1.5

+10

Full

−1.5 +0.6

+2.75

Full ±2

Full ±35

25°C 0.7

Full

1.383 1.75

2.087

Full 7

Full 20

Full

0.88 0.9

0.92

Full

1.7 1.8

1.9

Full

1.7 1.8

1.9

Full 175 190

Full 60 67

Full 423 460

Full 85

Full 15 27

Min

14

−6

−6

−3.1

1.383

0.87

AD9644-155

Typ Max

Guaranteed

±2.2

−1.5

±0.3

±0.55

±11

+4

±0.55

±1.25

+1.5

+0.75

+9

+5

±2

±144

0.7

1.75 2.087

5

20

0.9 0.93

1.7 1.8

1.7 1.8

226

89

567

168

18

1.9

1.9

242

97

610

27

Unit

Bits

mV

% FSR

LSB

LSB

LSB

LSB

mV

% FSR

ppm/°C

ppm/°C

LSB rms

V p-p

pF

kΩ

V

V

V

mA

mA

mW

mW

mW

1 Measured with a low input frequency, full-scale sine wave.

2 Input capacitance refers to the effective capacitance between one differential input pin and AGND.

3 Standby power is measured with a dc input and with the CLK pins inactive (set to AVDD or AGND).

Rev. C | Page 4 of 44

5 Page

AD9644

ABSOLUTE MAXIMUM RATINGS

Table 6.

Parameter

ELECTRICAL

AVDD to AGND

DRVDD to AGND

VIN+A/VIN+B, VIN−A/VIN−B to AGND

CLK+, CLK− to AGND

SYNC to AGND

VCMA, VCMB to AGND

CSB to AGND

SCLK to AGND

SDIO to AGND

PDWN to AGND

DOUT+A, DOUT0−A, DOUT0+B,

DOUT−B to AGND

DSYNC+A, DSYNC−A, DSYNC+B,

DSYNC−B to AGND

ENVIRONMENTAL

Operating Temperature Range

(Ambient)

Maximum Junction Temperature

Under Bias

Storage Temperature Range

(Ambient)

Rating

−0.3 V to +2.0 V

−0.3 V to +2.0V

−0.3 V to AVDD + 0.2 V

−0.3 V to AVDD + 0.2 V

−0.3 V to AVDD + 0.2 V

−0.3 V to AVDD + 0.2 V

−0.3 V to DRVDD + 0.2 V

−0.3 V to DRVDD + 0.2 V

−0.3 V to DRVDD + 0.2 V

−0.3 V to DRVDD + 0.2 V

−0.3 V to DRVDD + 0.2 V

−0.3 V to DRVDD + 0.2 V

−40°C to +85°C

150°C

−65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Data Sheet

THERMAL CHARACTERISTICS

The exposed paddle must be soldered to the ground plane for

the LFCSP package. Soldering the exposed paddle to the PCB

increases the reliability of the solder joints and maximizes the

thermal capability of the package.

Table 7. Thermal Resistance

Package Type

Airflow

Velocity

(m/sec)

48-Lead LFCSP

7 mm × 7 mm

(CP-48-8)

0

1.0

2.5

θJA1, 2

25

22

20

θJC1, 3

2

θJB1, 4

14

Unit

°C/W

°C/W

°C/W

1 Per JEDEC 51-7, plus JEDEC 25-5 2S2P test board.

2 Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

3 Per MIL-STD 883, Method 1012.1.

4 Per JEDEC JESD51-8 (still air).

Typical θJA is specified for a 4-layer PCB with a solid ground

plane. As shown Table 7, airflow improves heat dissipation,

which reduces θJA. In addition, metal in direct contact with the

package leads from metal traces, through holes, ground, and

power planes, reduces θJA.

ESD CAUTION

Rev. C | Page 10 of 44

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD9644.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9640 | Dual Analog-to-Digital Converter | Analog Devices |

| AD9641 | 1.8V Serial Output Analog-to-Digital Converter | Analog Devices |

| AD9642 | 1.8 V Analog-to-Digital Converter | Analog Devices |

| AD9643 | 1.8 V Dual Analog-to-Digital Converter | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |