|

|

PDF AD9516-5 Data sheet ( Hoja de datos )

| Número de pieza | AD9516-5 | |

| Descripción | 14-Output Clock Generator | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9516-5 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

FEATURES

Low phase noise, phase-locked loop (PLL)

External VCO/VCXO to 2.4 GHz optional

1 differential or 2 single-ended reference inputs

Reference monitoring capability

Automatic revertive and manual reference

switchover/holdover modes

Accepts LVPECL, LVDS, or CMOS references to 250 MHz

Programmable delays in path to PFD

Digital or analog lock detect, selectable

Six 1.6 GHz LVPECL outputs, arranged in 3 groups

Each group shares a 1-to-32 divider with coarse phase delay

Additive output jitter: 225 fs rms

Channel-to-channel skew paired outputs of <10 ps

Four 800 MHz LVDS outputs, arranged in 2 groups

Each group has 2 cascaded 1-to-32 dividers with coarse

phase delay

Additive output jitter: 275 fs rms

Fine delay adjust (Δt) on each LVDS output

Each LVDS output can be reconfigured as two 250 MHz

CMOS outputs

Automatic synchronization of all outputs on power-up

Manual output synchronization available

Available in 64-lead LFCSP

APPLICATIONS

Low jitter, low phase noise clock distribution

10/40/100 Gb/sec networking line cards, including SONET,

Synchronous Ethernet, OTU2/3/4

Forward error correction (G.710)

Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs

High performance wireless transceivers

ATE and high performance instrumentation

GENERAL DESCRIPTION

The AD9516-51 provides a multi-output clock distribution function

with subpicosecond jitter performance, along with an on-chip PLL

that can be used with an external VCO/VCXO of up to 2.4 GHz.

The AD9516-5 emphasizes low jitter and phase noise to

maximize data converter performance, and it can benefit other

applications with demanding phase noise and jitter requirements.

14-Output Clock Generator

AD9516-5

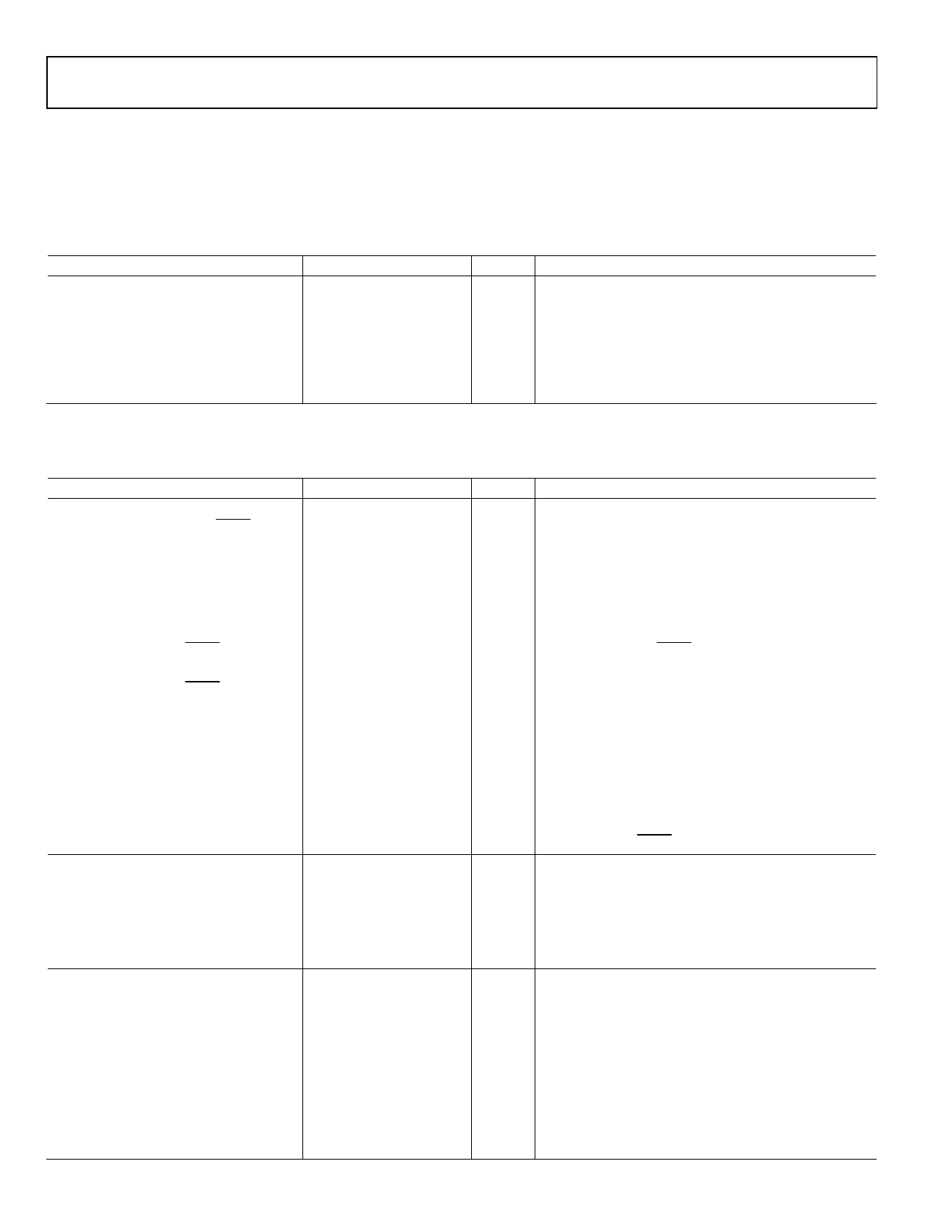

FUNCTIONAL BLOCK DIAGRAM

CP

REFIN

REFIN

REF1

REF2

STATUS

MONITOR

CLK

CLK

DIVIDER

AND MUXes

DIV/Φ

LVPECL

DIV/Φ

LVPECL

DIV/Φ

DIV/Φ

DIV/Φ

DIV/Φ

DIV/Φ

LVPECL

∆t

∆t

LVDS/CMOS

∆t

∆t

LVDS/CMOS

SERIAL CONTROL PORT

AND

DIGITAL LOGIC

AD9516-5

OUT0

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

OUT8

OUT9

Figure 1.

The AD9516-5 features six LVPECL outputs (in three pairs)

and four LVDS outputs (in two pairs). Each LVDS output can

be reconfigured as two CMOS outputs. The LVPECL outputs

operate to 1.6 GHz, the LVDS outputs operate to 800 MHz, and

the CMOS outputs operate to 250 MHz.

Each pair of outputs has dividers that allow both the divide ratio

and coarse delay (or phase) to be set. The range of division for

the LVPECL outputs is 1 to 32. The LVDS/CMOS outputs allow

a range of divisions up to a maximum of 1024.

The AD9516-5 is available in a 64-lead LFCSP and can be

operated from a single 3.3 V supply. An external VCO, which

requires an extended voltage range, can be accommodated by

connecting the charge pump supply (VCP) to 5.5 V. A separate

LVPECL power supply can be from 2.375 V to 3.6 V (nominal).

The AD9516-5 is specified for operation over the industrial

range of −40°C to +85°C.

For applications requiring an integrated EEPROM, or needing

additional outputs, the AD9520-5 and AD9522-5 are available.

1 AD9516 is used throughout the data sheet to refer to all members of the AD9516

family. However, when AD9516-5 is used, it refers to that specific member of the

AD9516 family.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113 ©2009–2011 Analog Devices, Inc. All rights reserved.

1 page

AD9516-5

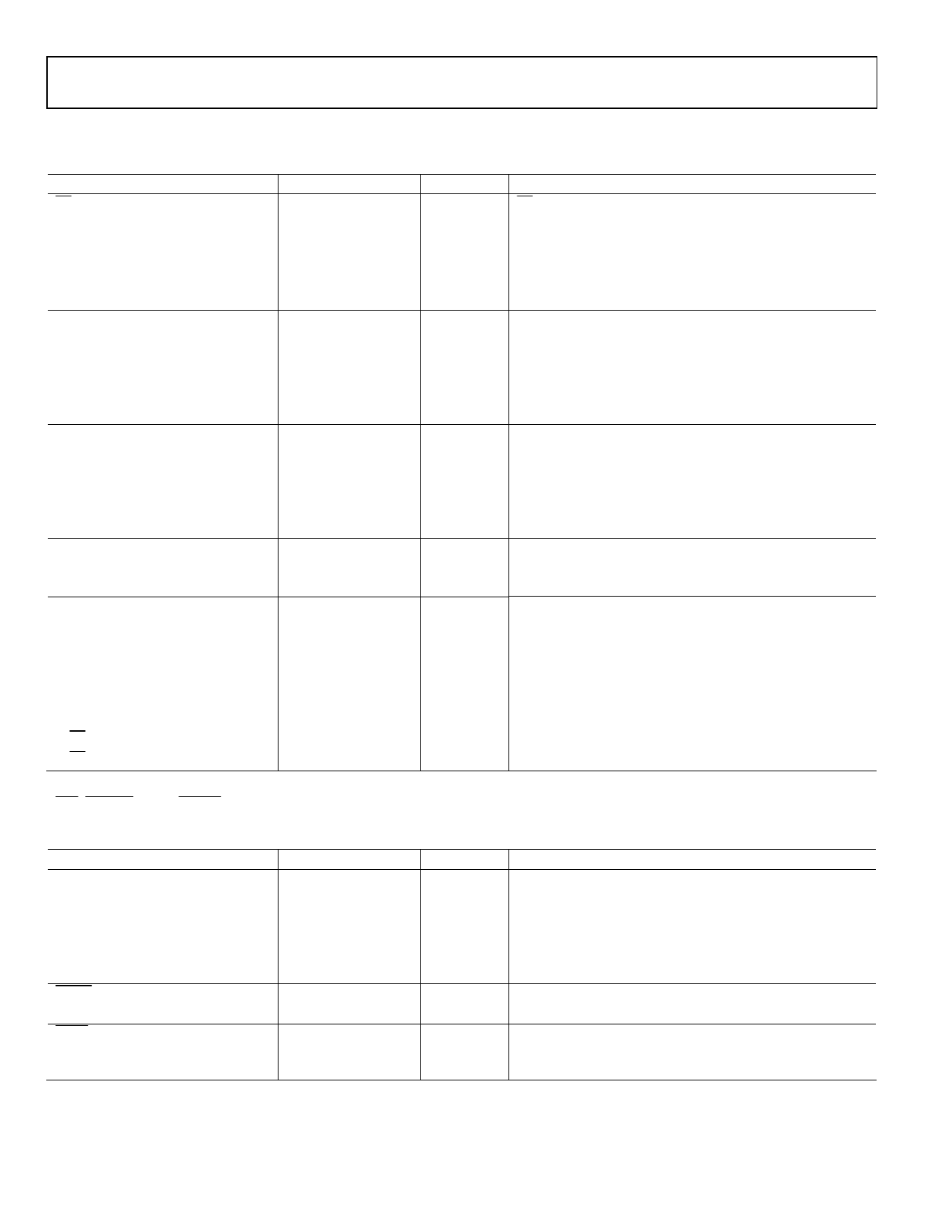

SPECIFICATIONS

Typical is given for VS = VS_LVPECL = 3.3 V ± 5%; VS ≤ VCP ≤ 5.25 V; TA = 25°C; RSET = 4.12 kΩ; CPRSET = 5.1 kΩ, unless otherwise noted.

Minimum and maximum values are given over full VS and TA (−40°C to +85°C) variation.

POWER SUPPLY REQUIREMENTS

Table 1.

Parameter

VS

VS_LVPECL

VCP

RSET Pin Resistor

CPRSET Pin Resistor

Min Typ Max Unit

3.135 3.3

3.465 V

2.375

VS V

VS 5.25 V

4.12 kΩ

2.7 5.1 10 kΩ

Test Conditions/Comments

3.3 V ± 5%

Nominally 2.5 V to 3.3 V ± 5%

Nominally 3.3 V to 5.0 V ± 5%

Sets internal biasing currents; connect to ground

Sets internal CP current range, nominally 4.8 mA

(CP_lsb = 600 μA); actual current can be calculated by:

CP_lsb = 3.06/CPRSET; connect to ground

PLL CHARACTERISTICS

Table 2.

Parameter

REFERENCE INPUTS

Differential Mode (REFIN, REFIN)

Input Frequency

Input Sensitivity

Self-Bias Voltage, REFIN

Self-Bias Voltage, REFIN

Input Resistance, REFIN

Input Resistance, REFIN

Dual Single-Ended Mode (REF1, REF2)

Input Frequency (AC-Coupled)

Input Frequency (DC-Coupled)

Input Sensitivity (AC-Coupled)

Input Logic High

Input Logic Low

Input Current

Input Capacitance

PHASE/FREQUENCY DETECTOR (PFD)

PFD Input Frequency

Antibacklash Pulse Width

CHARGE PUMP (CP)

ICP Sink/Source

High Value

Low Value

Absolute Accuracy

CPRSET Range

ICP High Impedance Mode Leakage

Sink-and-Source Current Matching

ICP vs. CPV

ICP vs. Temperature

Min

0

1.35

1.30

4.0

4.4

20

0

2.0

−100

Typ Max Unit

Test Conditions/Comments

Differential mode (can accommodate single-ended

input by ac grounding undriven input)

250 MHz

Frequencies below about 1 MHz should be dc-coupled;

be careful to match VCM (self-bias voltage)

250 mV p-p PLL figure of merit (FOM) increases with increasing slew

rate; see Figure 13

1.60 1.75 V

Self-bias voltage of REFIN1

1.50 1.60 V

Self-bias voltage of REFIN1

4.8 5.9 kΩ

Self-biased1

5.3 6.4 kΩ

Self-biased1

Two single-ended CMOS-compatible inputs

250 MHz

Slew rate > 50 V/μs

250 MHz

Slew rate > 50 V/μs; CMOS levels

0.8 V p-p Should not exceed VS p-p

V

0.8 V

+100 μA

2 pF Each pin, REFIN/REFIN (REF1/REF2)

100 MHz

Antibacklash pulse width = 1.3 ns, 2.9 ns

45 MHz Antibacklash pulse width = 6.0 ns

1.3 ns Register 0x017[1:0] = 01b

2.9 ns Register 0x017[1:0] = 00b; Register 0x017[1:0] = 11b

6.0 ns Register 0x017[1:0] = 10b

4.8 mA

0.60 mA

2.5 %

2.7/10

kΩ

1 nA

2%

1.5 %

2%

Rev. A | Page 4 of 76

Programmable

With CPRSET = 5.1 kΩ

CPV = VCP/2

0.5 < CPV < VCP − 0.5 V

0.5 < CPV < VCP − 0.5 V

VCP = VCP/2 V

5 Page

AD9516-5

SERIAL CONTROL PORT

Table 10.

Parameter

Min Typ Max Unit

CS (INPUT)

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8 V

Input Logic 1 Current

3 μA

Input Logic 0 Current

110 μA

Input Capacitance

2 pF

SCLK (INPUT)

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8 V

Input Logic 1 Current

110 μA

Input Logic 0 Current

1 μA

Input Capacitance

2 pF

SDIO (WHEN INPUT)

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8 V

Input Logic 1 Current

10 nA

Input Logic 0 Current

20 nA

Input Capacitance

2 pF

SDIO, SDO (OUTPUTS)

Output Logic 1 Voltage

2.7

V

Output Logic 0 Voltage

0.4 V

TIMING

Clock Rate (SCLK, 1/tSCLK)

25 MHz

Pulse Width High, tHIGH

Pulse Width Low, tLOW

SDIO to SCLK Setup, tDS

SCLK to SDIO Hold, tDH

SCLK to Valid SDIO and SDO, tDV

CS to SCLK Setup and Hold, tS, tH

16

16

2

1.1

2

ns

ns

ns

ns

8 ns

ns

CS Minimum Pulse Width High, tPWH 3

ns

Test Conditions/Comments

CS has an internal 30 kΩ pull-up resistor

SCLK has an internal 30 kΩ pull-down resistor

PD, RESET, AND SYNC PINS

Table 11.

Parameter

INPUT CHARACTERISTICS

Logic 1 Voltage

Logic 0 Voltage

Logic 1 Current

Logic 0 Current

Capacitance

RESET TIMING

Pulse Width Low

SYNC TIMING

Pulse Width Low

Min Typ Max

2.0

0.8

110

1

2

50

1.5

Unit Test Conditions/Comments

Each of these pins has an internal 30 kΩ pull-up resistor

V

V

μA

μA

pF

ns

High speed High speed clock is CLK input signal

clock cycles

Rev. A | Page 10 of 76

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD9516-5.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9516-0 | 14-Output Clock Generator | Analog Devices |

| AD9516-1 | 14-Output Clock Generator | Analog Devices |

| AD9516-2 | 14-Output Clock Generator | Analog Devices |

| AD9516-3 | 14-Output Clock Generator | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |