|

|

PDF AD7472 Data sheet ( Hoja de datos )

| Número de pieza | AD7472 | |

| Descripción | 4 mW 10-Bit/12-Bit Parallel ADCs | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD7472 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

a

1.75 MSPS, 4 mW

10-Bit/12-Bit Parallel ADCs

AD7470/AD7472

FEATURES

Specified for VDD of 2.7 V to 5.25 V

1.75 MSPS for AD7470 (10-Bit)

1.5 MSPS for AD7472 (12-Bit)

Low Power

AD7470: 3.34 mW Typ at 1.5 MSPS with 3 V Supplies

7.97 mW Typ at 1.75 MSPS with 5 V Supplies

AD7472: 3.54 mW Typ at 1.2 MSPS with 3 V Supplies

8.7 mW Typ at 1.5 MSPS with 5 V Supplies

Wide Input Bandwidth

70 dB Typ SNR at 500 kHz Input Frequency

Flexible Power/Throughput Rate Management

No Pipeline Delays

High Speed Parallel Interface

Sleep Mode: 50 nA Typ

24-Lead SOIC and TSSOP Packages

FUNCTIONAL BLOCK DIAGRAM

AVDD DVDD

REF IN

VDRIVE

10-/12-BIT

VIN

T/H

SUCCESSIVE

APPROXIMATION

OUTPUT

DRIVERS

ADC

DB9 (DB11)

DB0

CONVST

CONTROL

LOGIC

AD7470/AD7472

CLK IN

CS

RD

BUSY

GENERAL DESCRIPTION

The AD7470/AD7472 are 10-bit/12-bit high speed, low power,

successive-approximation ADCs. The parts operate from a

single 2.7 V to 5.25 V power supply and feature throughput rates

up to 1.5 MSPS for the 12-bit AD7472 and up to 1.75 MSPS for

the 10-bit AD7470. The parts contain a low noise, wide band-

width track/hold amplifier that can handle input frequencies in

excess of 1 MHz.

The conversion process and data acquisition are controlled

using standard control inputs allowing easy interfacing to

microprocessors or DSPs. The input signal is sampled on the

falling edge of CONVST and conversion is also initiated at

this point. The BUSY goes high at the start of conversion and

goes low 531.66 ns after falling edge of CONVST (AD7472 with

a clock frequency of 26 MHz) to indicate that the conversion is

complete. There are no pipelined delays associated with the part.

The conversion result is accessed via standard CS and RD sig-

nals over a high speed parallel interface.

The AD7470/AD7472 uses advanced design techniques to

achieve very low power dissipation at high throughput rates. With

3 V supplies and 1.5 MSPS throughput rate, the AD7470 typi-

cally consumes, on average, just 1.1 mA. With 5 V supplies and

1.75 MSPS, the average current consumption is typically

1.6 mA. The part also offers flexible power/throughput rate

management. Operating the AD7470 with 3 V supplies and

500 kSPS throughput reduces the current consumption to 713 µA.

At 5 V supplies and 500 kSPS, the part consumes 944 µA.

AGND DGND

AD7470 IS A 10-BIT PART WITH DB0 TO DB9 AS OUTPUTS.

AD7472 IS A 12-BIT PART WITH DB0 TO DB11 AS OUTPUTS.

It is also possible to operate the parts in an auto sleep mode,

where the part wakes up to do a conversion and automatically

enters sleep mode at the end of conversion. Using this method

allows very low power dissipation numbers at lower throughput

rates. In this mode, the AD7472 can be operated with 3 V sup-

plies at 100 kSPS, and consume an average current of just 124 µA.

At 5 V supplies and 100 kSPS, the average current consumption

is 171 µA.

The analog input range for the part is 0 to REF IN. The +2.5 V

reference is applied externally to the REF IN pin. The conver-

sion rate is determined by the externally-applied clock.

PRODUCT HIGHLIGHTS

1. High Throughput with Low Power Consumption. The

AD7470 offers 1.75 MSPS throughput and the AD7472

offers 1.5 MSPS throughput rates with 4 mW power

consumption.

2. Flexible Power/Throughput Rate Management. The conver-

sion rate is determined by an externally-applied clock allow-

ing the power to be reduced as the conversion rate is reduced.

The part also features an auto sleep mode to maximize power

efficiency at lower throughput rates.

3. No Pipeline Delay. The part features a standard successive-

approximation ADC with accurate control of the sampling

instant via a CONVST input and once off conversion

control.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2000

1 page

ABSOLUTE MAXIMUM RATINGS1

(TA = +25°C unless otherwise noted)

AVDD to AGND/DGND . . . . . . . . . . . . . . . . . –0.3 V to +7 V

DVDD to AGND/DGND . . . . . . . . . . . . . . . . . –0.3 V to +7 V

VDRIVE to AGND/DGND . . . . . . . . . . . . . . . . –0.3 V to +7 V

AVDD to DVDD . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

VDRIVE to DVDD . . . . . . . . . . . . . . . –0.3 V to DVDD + 0.3 V

AGND TO DGND . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

Analog Input Voltage to AGND . . . –0.3 V to AVDD + 0.3 V

Digital Input Voltage to DGND . . . –0.3 V to DVDD + 0.3 V

REF IN to AGND . . . . . . . . . . . . . . –0.3 V to AVDD + 0.3 V

Input Current to Any Pin Except Supplies2 . . . . . . . . ± 10 mA

Operating Temperature Range

Commercial (A and B Version) . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . .+150°C

SOIC, TSSOP Package Dissipation . . . . . . . . . . . . . +450 mW

θJA Thermal Impedance . . . . . . . . . . . . . . . 75°C/W (SOIC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115°C/W (TSSOP)

θJC Thermal Impedance . . . . . . . . . . . . . . . 25°C/W (SOIC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35°C/W (TSSOP)

Lead Temperature, Soldering

Vapor Phase (60 secs) . . . . . . . . . . . . . . . . . . . . . . .+215°C

Infrared (15 secs) . . . . . . . . . . . . . . . . . . . . . . . . . . .+220°C

NOTES

1Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2Transient currents of up to 100 mA will not cause SCR latch-up.

AD7470/AD7472

PIN CONFIGURATIONS

DB7 1

24 DB6

DB8 2

23 DB5

(MSB) DB9 3

22 DB4

AVDD 4

21 VDRIVE

REF IN 5 AD7470 20 DVDD

VIN 6 TOP VIEW 19 DGND

AGND 7 (Not to Scale) 18 DB3

CS 8

17 DB2

RD 9

16 DB1

CONVST 10

15 DB0 (LSB)

CLKIN 11

14 NC

BUSY 12

13 NC

NC = NO CONNECT

DB9 1

24 DB8

DB10 2

23 DB7

(MSB) DB11 3

22 DB6

AVDD 4

21 VDRIVE

REF IN 5 AD7472 20 DVDD

VIN 6 TOP VIEW 19 DGND

AGND 7 (Not to Scale) 18 DB5

CS 8

17 DB4

RD 9

16 DB3

CONVST 10

15 DB2

CLKIN 11

14 DB1

BUSY 12

13 DB0 (LSB)

ORDERING GUIDE

Model

Temperature

Range

Resolution

(Bits)

Package

Options1

AD7470ARU

AD7472AR

AD7472BR

AD7472ARU

AD7472BRU

EVAL-AD7470CB2

EVAL-AD7472CB2

EVAL-CONTROL BOARD3

HSC-INTERFACE BOARD

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

10

12

12

12

12

RU-24

R-24

R-24

RU-24

RU-24

Evaluation Board

Evaluation Board

Controller Board

Evaluation High Speed Interface Board

NOTES

1R = SOIC; RU = TSSOP.

2This can be used as a stand-alone evaluation board or in conjunction with the EVAL-CONTROL BOARD for evaluation/demonstration purposes.

3This board is a complete unit allowing a PC to control and communicate with all Analog Devices evaluation boards ending in the CB designators.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7470/AD7472 features proprietary ESD protection circuitry, permanent dam-

age may occur on devices subjected to high energy electrostatic discharges. Therefore, proper

ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

REV. A

–5–

5 Page

CONVST

BUSY

CS

RD

DBx

tCONVERT

AD7470/AD7472

tWAKEUP

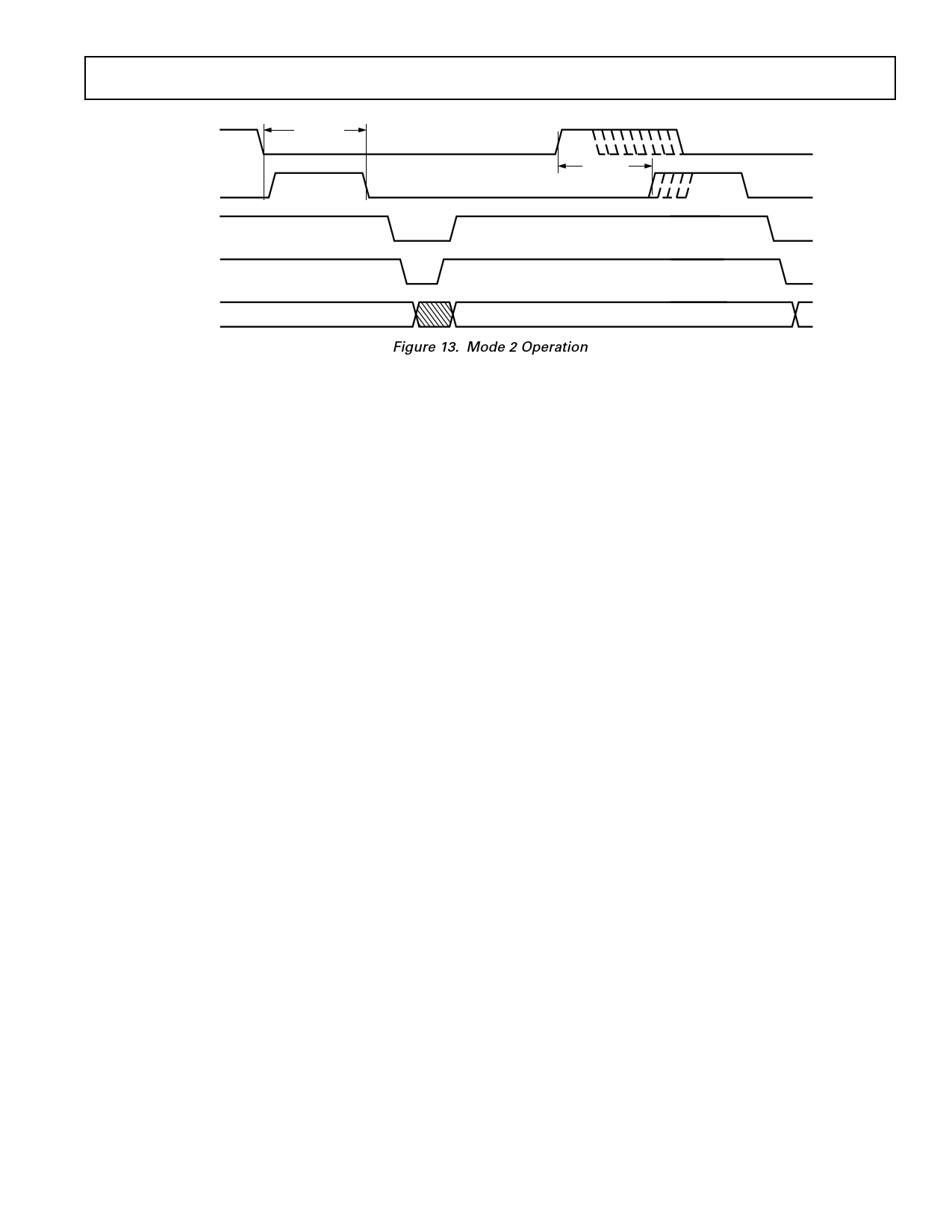

Figure 13. Mode 2 Operation

OPERATING MODES

The AD7470 and AD7472 have two possible modes of opera-

tion depending on the state of the CONVST pulse at the end of

a conversion, Mode 1 and Mode 2. There is a continuous clock

on the CLK IN pin.

Mode 1 (High Speed Sampling)

In this mode of operation the CONVST pulse is brought high

before the end of conversion i.e., before the BUSY goes low (see

Figure 10). If the CONVST pin is brought from high to low while

BUSY is high, the conversion is restarted. When operating in

this mode a new conversion should not be initiated until 135 ns

after BUSY goes low. This acquisition time allows the track/

hold circuit to accurately acquire the input signal. As mentioned

earlier, a read should not be done during a conversion. This

mode facilitates the fastest throughput times for the AD7470/

AD7472.

Mode 2 (Sleep Mode)

Figure 13 shows AD7470/AD7472 in Mode 2 operation where

the ADC goes into sleep mode after conversion. The CONVST

line is brought low to initiate a conversion and remains low until

after the end of conversion. If CONVST goes high and low

again while BUSY is high, the conversion is restarted. Once the

BUSY line goes from a high to a low, the CONVST line has its

status checked and, if low, the part enters sleep mode.

The device wakes up again on the rising edge of the CONVST

signal. There is a wake-up time of typically 1 µs after the rising

edge of CONVST before the BUSY line can go high to indicate

start of conversion. BUSY will only go high once CONVST goes

low. The CONVST line can go from a high to a low during this

wake-up time, but the conversion will still not be initiated until

after the 1 µs wake-up time. Superior power performance can be

achieved in this mode of operation by waking up the AD7470

and AD7472 only to carry out a conversion.

Burst Mode

Burst mode on the AD7470/AD7472 is a subsection of Mode 1

and Mode 2, the clock is noncontinuous. Figure 12 shows how

the ADC works in burst mode for Mode 2. The clock needs

only to be switched on during conversion, minimum of 12 clock

cycles for the AD7470 and 14 clock cycles for the AD7472. As

the clock is off during nonconverting intervals, system power is

saved. The BUSY signal can be used to gate the CLK IN pulses.

The ADC does not begin the conversion process until the first

CLK IN rising edge after BUSY goes high. The clock needs to

start less than two clock cycles away from the CONVST active

edge otherwise INL deteriorates; e.g., if the clock frequency is

28 MHz the clock must start within 71.4 ns of CONVST going

low. In Figure 12 the A-D converter section is put into sleep

mode once conversion is completed and on the rising edge of

CONVST it is woken up again; the user must be wary of the

wake-up time as this will reduce the sampling rate of the ADC.

VDRIVE

The VDRIVE pin is used as the voltage supply to the output driv-

ers and is a separate supply from AVDD and DVDD. The purpose

of using a separate supply for the output drivers is that the user

can vary the output high voltage, VOH, from the VDD supply to

the AD7470/AD7472. For example, if AVDD and DVDD is using

a 5 V supply, the VDRIVE pin can be powered from a 3 V supply.

The ADC has better dynamic performance at 5 V than at 3 V,

so operating the part at 5 V, while still being able to interface to

3 V parts, pushes the AD7470/AD7472 to the top bracket of

high performance 10-bit/12-bit A/Ds. Of course, the ADC can

have its VDRIVE and DVDD pins connected together and be pow-

ered from a 3 V or 5 V supply.

All outputs are powered from VDRIVE. These are all the data out

pins and the BUSY pin. The CONVST, CS, RD and CLK IN

signals are related to the DVDD voltage.

POWER-UP

It is recommended that the user performs a dummy conversion

after power-up, as the first conversion result could be incorrect.

This also ensures that the parts is in the correct mode of opera-

tion. The recommended power-up sequence is as follows:

1 > GND

2 > VDD

3 > VDRIVE

4 > Digital Inputs

5 > REF IN

6 > VIN

Power vs. Throughput

The two modes of operation for the AD7470 and AD7472 will

produce different power versus throughput performances, Mode

1 and Mode 2; see Operating Modes section of the data sheet

for more detailed descriptions of these modes. Mode 2 is the

Sleep Mode of the part and it achieves the optimum power

performance.

REV. A

–11–

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet AD7472.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD7470 | 4 mW 10-Bit/12-Bit Parallel ADCs | Analog Devices |

| AD7472 | 4 mW 10-Bit/12-Bit Parallel ADCs | Analog Devices |

| AD7475 | 1 MSPS / 12-Bit ADCs | Analog Devices |

| AD7476 | 1 MSPS/ 12-/10-/8-Bit ADCs in 6-Lead SOT-23 | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |