|

|

PDF 8V97053 Data sheet ( Hoja de datos )

| Número de pieza | 8V97053 | |

| Descripción | Low Power Wideband Fractional RF Synthesizer / PLL | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 8V97053 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Low Power Wideband Fractional RF

Synthesizer / PLL

8V97053

Datasheet

General Description

The 8V97053 is a high performance Wideband RF Synthesizer / PLL

optimized for use as the local oscillator (LO) in Multi-Carrier,

Multi-mode FDD & TDD Base Station radio card. It is offered in a

compact 5x5, 32-VFQFN.

The 8V97053 Wideband RF Synthesizer / PLL offers a default

Fractional Mode with the option to use it with an Integer mode. It

requires an external loop filter.

The 8V97053 with integrated Voltage Controlled Oscillator (VCO)

supports output frequencies from 34.375MHz to 4400MHz and

maintains superior phase noise and spurious performance.

RF_OUT[A:B] output drivers have independently programmable

output power ranging from –4dBm to +7dBm. The RF_OUT outputs

can be muted. The mute function is accessible via a SPI command

or mute pin.

The operation of the 8V97053 is controlled by writing to registers

through a 3-wire SPI interface. The 8V97053 also has an additional

option that allows users to read back values from registers by

configuring the MUX_OUT pin as a SDO for the SPI interface. The

SPI interface is compatible with 1.8V logic and tolerant to 3.3V.

In multi-service base stations, very low noise oscillators are required

to generate a large variety of frequencies to the mixers while

maintaining excellent phase noise performance and low power. The

8V97053 offers a large tuning range capable of providing multi-band

local oscillator (LO) frequency synthesis in multi-mode base stations,

thus limiting the use of multiple narrow band RF Synthesizers and

reducing the BOM complexity and cost. The device can operate over

-40°C to +85°C industrial temperature range.

Features

• Dual Differential Outputs

• Output frequency range: 34.375MHz to 4400MHz (continuous

range)

• RF Output Divide by 1, 2, 4, 8, 16, 32, 64

• Open Drain Outputs (see Output Distribution Section)

• Fractional-N synthesizer (also supports Integer-N mode)

• 16-bit integer and 12-bit fractional

(16-bit fractional when using the extended registers)

• 3- or 4-wire SPI interface (compatible with 3.3V and 1.8V)

• Single 3.3V supply

• Logic compatibility: 1.8V

• Programmable output power level: -4dBm to +5dBm

(up to +7 when using the extended registers)

• Mute Function

• Ultra low PN for 1.65GHz LO: -142.21dBc/Hz @ 1MHz Offset,

(typical)

• Lock Detect Indicators

• Input Reference frequency: 5MHz to 310MHz

• 32-Lead, 5x5 VFQFN package

• Automatic VCO band selection (Autocal feature)

• -40°C to +85°C ambient operating temperature

• Lead-free (RoHS 6) packaging

Applications

• Wireless Infrastructure

• Test Equipment

• CATV Equipment

• Military and Aerospace

• Wireless LAN

• Clock Generation

©2016 Integrated Device Technology, Inc.

1

September 22, 2016

1 page

8V97053 Datasheet

Phase Noise (Closed-Loop) at 1.76GHz (3.3V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Phase Noise (Closed-Loop) at 2.05GHz (3.3V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Phase Noise (Open-Loop) at 745MHz (3.3V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Phase Noise Performance (Open-Loop) at 1.1GHz (3.3V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Phase Noise Performance (Open-Loop) at 1.65GHz (3.3V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Phase Noise Performance (Open-Loop) at 2.3GHz (3.3V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Phase Noise Performance (Open-Loop) at 3.8GHz (3.3V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Phase Noise Performance (Open-Loop) at 4.4GHz (3.3V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Applications Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Loop Filter Calculations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

2nd Order Loop Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Figure 11. Typical 2nd Order Loop Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

3rd Order Loop Filter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 12. Typical 3rd Order Loop Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Recommendations for Unused Input and Output Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Schematic Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Figure 13A. An 8V97053 General Application Schematic Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Figure 13B. Schematic Example for Driving Single Ended Mixer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Power Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Table 16. Thermal Resistance JA for 32 Lead VFQFN, Forced Convection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Example 2: VCO Frequency Range = 2590MHz to 3624MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Reliability Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Table 17A. JA vs. Air Flow Table for a 32 lead VFQFN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Table 17B. JB vs. Air Flow Table for a 32 lead VFQFN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

32-Lead VFQFN Package Outline and Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

32-Lead VFQFN Package Outline and Package Dimensions (Continued) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Table 18. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Table 19. Pin 1 Orientation in Tape and Reel Packaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

©2016 Integrated Device Technology, Inc.

5

September 22, 2016

5 Page

8V97053 Datasheet

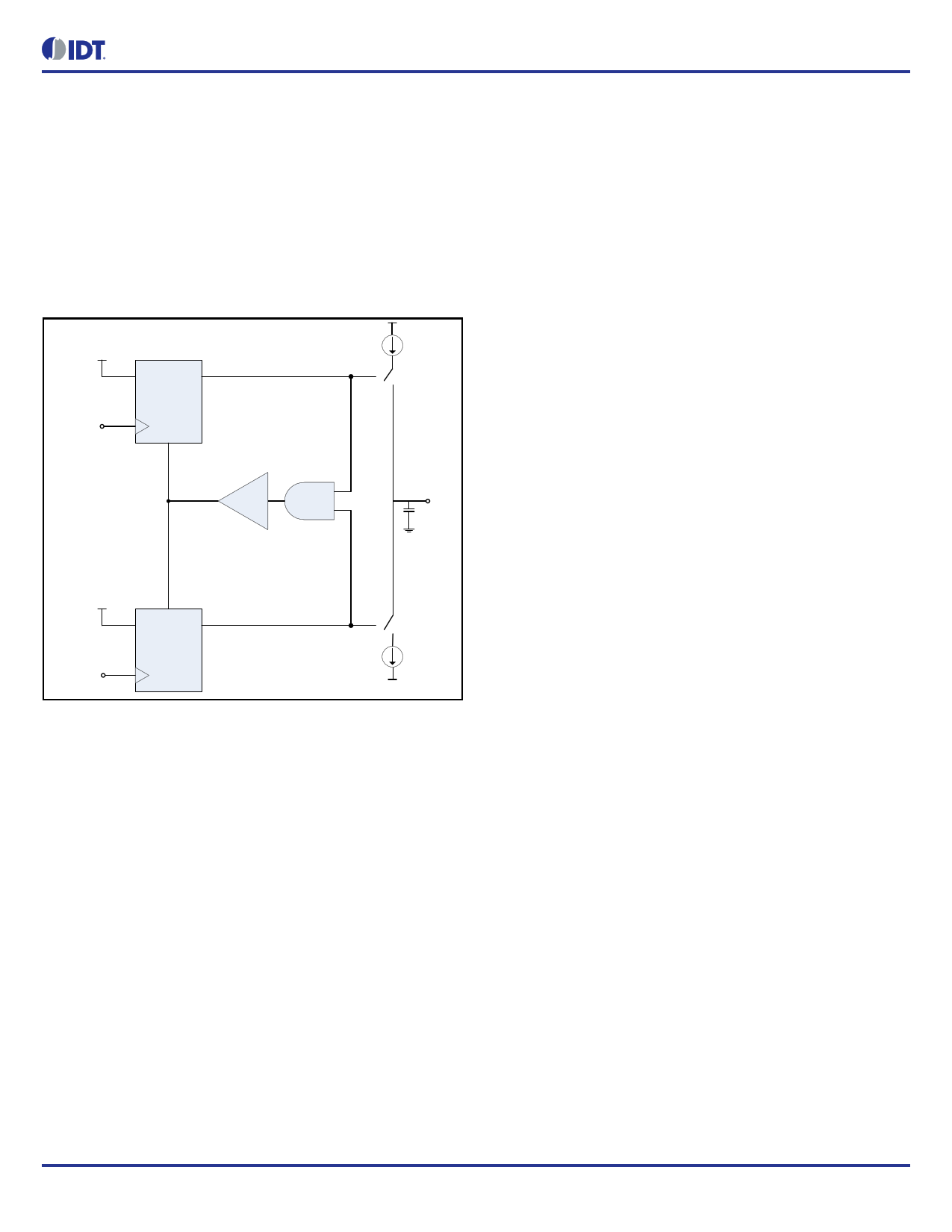

Phase and Frequency Detector (PFD) and Charge

Pump

The phase detector compares the outputs from the R counter and

from the N counter and generates an output corresponding to the

phase and frequency difference between the two inputs the PFD. The

charge pump current is programmable through the serial port (SPI)

to several different levels.

The PFD offers an anti-backlash function that helps to avoid any

dead zone in the PFD transfer function.

VDD

D1

Q1

REF_IN x (1+D)/R

ICP

Register 4) to 12-bits. The four additional band select divider bits

in Register 4 are the most significant bits of the divide value. For

proper VCO band selection, the PFD frequency divided by the

band select divide value must be 500kHz and 125kHz.

B.If choosing this second technique, the user must follow the

three following steps:

1. Disable the Phase Adjust function by setting the bit D28 In

Register 1 to 0, keep the PFD frequency lower than 125MHz,

and program the desired VCO frequency.

2. Enable the phase adjust function by setting

BAND_SEL_DISABLE (Bit D28 in Register 1) to 1.

3. Set the desired PFD frequency and program the relevant

R divider and N counter values.

In either technique, the Lock Detect Precision should be

programmed to be lower than the PFD period using the bit [D7] in

Register 2 and the bits [D27:D26] in Register 6 (Refer to Table 4A,

Page 9).

DELAY

CP_OUT

External Loop Filter

The 8V97053 requires an external loop filter. The design of that filter

is application specific. For additional information, refer to the

Applications Information section.

VDD

D1

Q1

FB

ICP

Figure 2. Simplified PFD Circuit using D-type Flip-flop

The Band Select logic operates between 125kHz and 500kHz. The

Band Select clock divider needs to be set to divide down the PFD

frequency to between 125kHz to 500kHz (logic maximum frequency).

PFD Frequency

The VCO Band Selection can be used while operating at PFD

frequencies up to 310MHz.

If the application requires the PFD frequency to be higher than

125MHz, the user can use one of the following two techniques

(Technique A is the recommended procedure):

A.The user can use the extended register ExtBndSelDiv[4:1] bits

(Bits[D6:D3]) in Register 6. These additional band select divider

bits extend the band select divider from 8-bits (available in

Phase Detector Polarity

The phase detector polarity is set by bit D6 in Register 2. This bit

should be set to 1 when using a passive loop filter or a non-inverting

active loop filter. If an inverting active filter is used, this bit should be

set to 0.

Charge Pump High-Impedance

In order to put the charge pump into three-state mode, the user must

set the bit D4 [CP HIGHZ] in Register 2 to 1. This bit should be set to

0 for normal operation.

Integrated Low Noise VCO

The VCO function of the 8V97053 consists in three separate VCOs.

This allows keeping narrow tuning ranges for the VCOs while offering

a large frequency tuning range for VCO core. Keeping narrow VCO

tuning ranges allows for lower VCO sensitivity (KVCO), which results

in the best possible VCO phase noise and spurious performance.

The user does not have to select the different VCO bands. The VCO

band select logic of the 8V97053 will automatically select the most

suitable band of operation at power up or when Register 0 is written.

©2016 Integrated Device Technology, Inc.

11

September 22, 2016

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 8V97053.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 8V97051 | Low Power Wideband Fractional RF Synthesizer / PLL | IDT |

| 8V97053 | Low Power Wideband Fractional RF Synthesizer / PLL | IDT |

| 8V97053L | Low Power Wideband Fractional RF Synthesizer / PLL | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |