|

|

PDF 8V49NS0312 Data sheet ( Hoja de datos )

| Número de pieza | 8V49NS0312 | |

| Descripción | Clock Generator | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 8V49NS0312 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

FemtoClock® NG Clock Generator

with 4 Dividers

8V49NS0312

Datasheet

General Description

The 8V49NS0312 is a Clock Generator with four output dividers:

three integer and one that is either integer or fractional. When used

with an external crystal, the 8V49NS0312 generates high perfor-

mance timing geared towards the communications and datacom

markets, especially for applications demanding extremely low phase

noise, such as 10, 40 and 100GE.

The 8V49NS0312 provides versatile frequency configurations and

output formats and is optimized to deliver excellent phase noise

performance. The device delivers an optimum combination of high

clock frequency and low phase noise performance, combined with

high power supply noise rejection.

The 8V49NS0312 supports two types of output levels: LVPECL or

LVDS on eleven of its outputs. In addition there is a single LVCMOS

output that has the option of providing a generated clock or acting as

a reference bypass output.

The device can be configured to deliver specific output

configurations under pin control only or additional configurations

through an I2C serial interface.

It is offered in a lead-free (RoHS6) 64-pin VFQFN package.

Features

▪ Eleven differential LVPECL, LVDS outputs with programmable

voltage swings

▪ One LVCMOS output

— Input reference maybe bypassed to this output

▪ The clock input operates in full differential mode (LVDS, LVPECL)

or single-ended LVCMOS mode

▪ Driven from a crystal or differential clock input

▪ 2.4-2.5GHz PLL frequency range supports Ethernet, SONET and

CPRI frequency plans

▪ Four Integer output dividers with a range of output divide ratios

(see Table 7)

▪ One Fractional Output divider can generate any desired output

frequency

▪ Support of output power-down

▪ Excellent clock output phase noise

Offset Output Frequency Single-side Band Phase Noise

100kHz

156.25MHz

-143dBc/Hz

▪ Phase Noise RMS, 156.25MHz, 12kHz to 20MHz integration

range: 110fs (maximum)

▪ Select configurations may be controlled via the use of control

input pins without need for serial port access

▪ LVCMOS compatible I2C serial interface gives access to

additional configurations either alone or in combination with the

control input pins

▪ Single 3.3V supply voltage

▪ Lead-free (RoHS 6) 64-pin VFQFN packaging

▪ -40°C to 85°C ambient operating temperature

©2016 Integrated Device Technology, Inc.

1

September 2, 2016

1 page

8V49NS0312 Datasheet

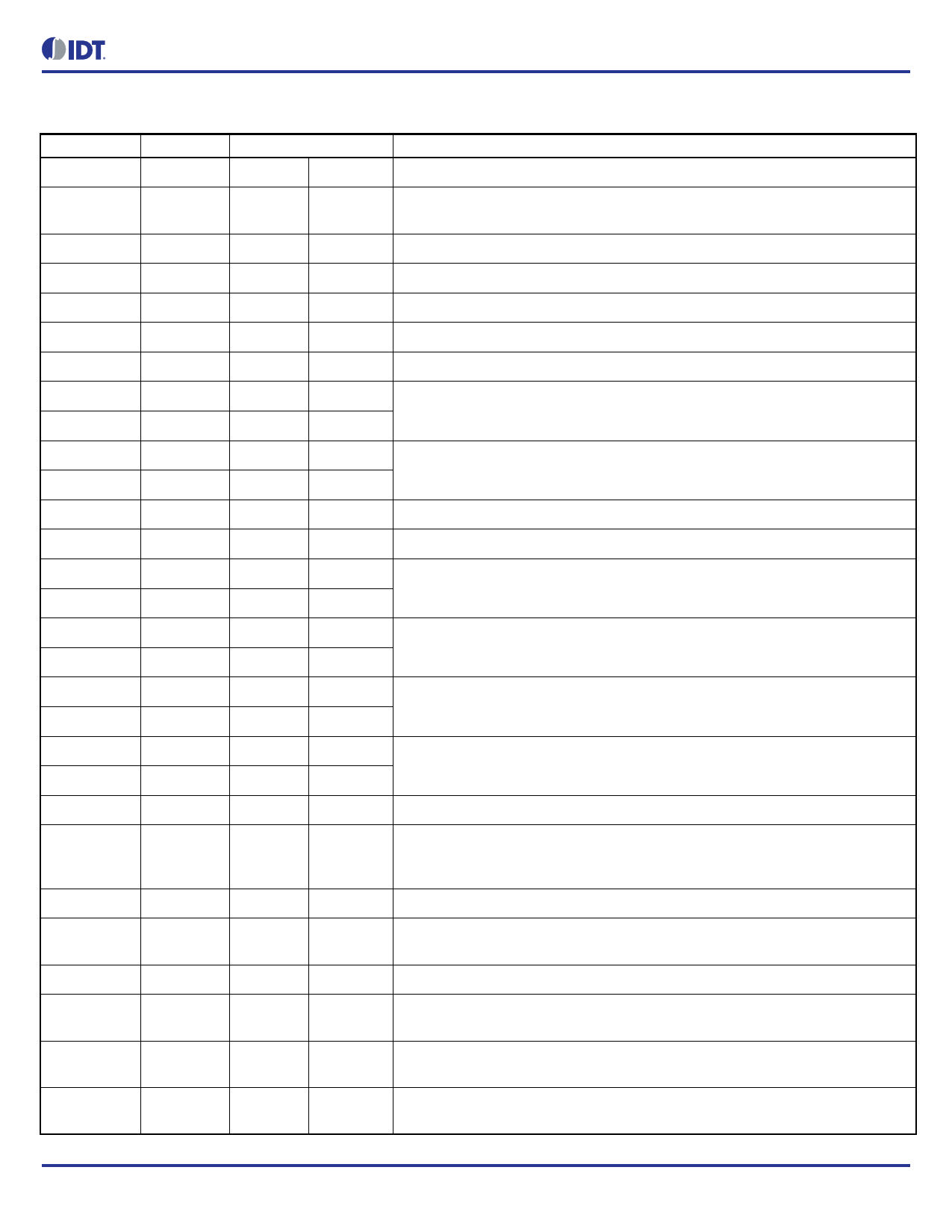

Table 1: Pin DescriptionsaCont.

Number

Name

Type

27

LFFR

Analog

Description

Ground return path pin for the PLL loop filter.

28 LFF Output

Loop filter/charge pump output for the FemtoClock NG PLL. Connect to the external

loop filter.

29

VCCA

Power

Analog Power Supply Voltage for VCO (3.3V).

30 nc - - No connect. Do not use.

31

VCC_CP

Power

32 ICP Analog

Analog Power Supply Voltage for PLL charge pump (3.3V).

Charge pump current input for PLL. Connect to LFF pin (28).

33

VCCOC

Power

34

nQC1

Output

35

QC1

Output

Power Supply Voltage for Output Bank C (3.3V).

Differential device clock output pair. LVPECL or LVDS with configurable amplitude.

36

nQC0

Output

37

QC0

Output

Differential device clock output pair. LVPECL or LVDS with configurable amplitude.

38

VCCOC

Power

39

VCCOA

Power

40

nQA3

Output

41

QA3

Output

Power Supply Voltage for Output Bank C (3.3V).

Power Supply Voltage for Output Bank A (3.3V).

Differential device clock output pair. LVPECL or LVDS with configurable amplitude.

42

nQA2

Output

43

QA2

Output

Differential device clock output pair. LVPECL or LVDS with configurable amplitude.

44

nQA1

Output

45

QA1

Output

Differential device clock output pair. LVPECL or LVDS with configurable amplitude.

46

nQA0

Output

47

QA0

Output

Differential device clock output pair. LVPECL or LVDS with configurable amplitude.

48

VCCOA

Power

Power Supply Voltage for Output Bank A (3.3V).

Selects Input Reference source. LVCMOS interface levels.

49

REF_SEL

Input

Pulldown 0 = Crystal input on pins OSCI, OSCO (default)

1 = Reference clock input on pins CLK, nCLK

50

VCC_CK

Power

Power Supply Voltage for input CLK, nCLK (3.3V).

51

nCLK

Input

Pullup/

Pulldown

Inverting differential clock input. Internal resistor bias to VCC_CK.

52

CLK

Input

Pulldown Non-inverting differential clock input.

53

FIN[1]

Input

Pullup /

Pulldown

Control Inputs for Input Reference Frequencies. 3-level signals. Refer to Table 5.

54

FIN[0]

Input

Pullup /

Pulldown

Control Inputs for Input Reference Frequencies. 3-level signals. Refer to Table 5.

55

CAPXTAL

Analog

Crystal oscillator circuit decoupling capacitor. Use a 4.7µF capacitor between the

CAPXTAL and the VEE terminals.

©2016 Integrated Device Technology, Inc.

5

September 2, 2016

5 Page

8V49NS0312 Datasheet

Fractional Output Divider (Bank D)

For the fractional output divider in Bank D, the output divide ratio is given by:

fOUT = -2------------F---I---N----T-----+------Ff-----V--R--2--C----2-A---O4------C-------------------F---D-----I--V------

Where,

▪ FINT = Integer Part: 5, 6, ...(24-1) - given by ND_FINT[3:0]

▪ FRAC = Fractional Part: 0, 1, 2, ...(224-1)- given by ND_FRAC[23:0]

▪ FDIV = post-divider: 1, 2 or 4- given by ND_DIVF[1:0]

This provides a frequency range of 20MHz to 312.5MHz.

Output Drivers

Each of the four output banks are provided with pin or register-controlled output drivers. Differential outputs may be individually selected as

LVDS, LVPECL or POWER-DOWN. When powered down, both outputs of the differential output pair will drive a logic-high level, and the

single-ended QD1output will be in Hi-Z state.

The differential outputs may individually choose one of several different output voltage swings: 350mV, 500mV or 750mV, measured

single-ended.

Note that under pin-control, all differential outputs within an output bank will assume the same configuration. Pin-control does not allow

configuration of individual outputs within a bank.

Pin Control of the Output Frequencies and Protocols

See Table 8, Table 9, Table 10, Table 11 and Table 12, for pin-control settings. All of the output frequencies assume fVCO = 2500MHz. With

different fVCO configurations, the pins may still be used to select the indicated divide ratios for each bank, but the fOUT will be different.

Note that the control pins do not affect the internal register values, but act directly on the output structures. So register values will not change

to match the control input pin selections.

Each output bank may be powered-up / down and enabled / disabled by register bits. In the disabled state, an output will drive a logic low level.

The default state is all outputs enabled. Pin-control does not require register access to enable the outputs. Additionally, individual outputs

within a bank may be powered up / down.

Table 8: Definition of Output Disabled / Power-down

OUTPUT CONDITION

QMNa

nQMNb

DISABLED (register-control only)

LOW

HIGH

POWER-DOWN (pin-control or register-control)

HIGH

HIGH

a. QMN refers to output pins QA[0:3], QB[0:3], QC[0:1] and QD0.

b. nQMN refers to output pins nQA[0:3], nQB[0:3], nQC[0:1] and nQD0.

QD1

LOW

Hi-Z

©2016 Integrated Device Technology, Inc.

11

September 2, 2016

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 8V49NS0312.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 8V49NS0312 | Clock Generator | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |