|

|

PDF DA7217 Data sheet ( Hoja de datos )

| Número de pieza | DA7217 | |

| Descripción | Ultra-Low Power Stereo Codec | |

| Fabricantes | Dialog Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DA7217 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DA7217

Ultra-Low Power Stereo Codec

General Description

DA7217 is a high-performance, low-power audio codec optimized for use in headsets or wearable

devices. It has differential headphone outputs for use inside headset devices, offering excellent left to

right channel separation and common mode noise rejection. DA7217 also has a stereo DAC to

headphone output path and ultra-low power operating modes to support always-on audio detect

applications.

DA7217 contains two analog microphone input paths, or up to four digital microphone input paths, or

a combination of both. The other chip in this family, the DA7218, has single-ended headphone

outputs, and has been designed with headphone detect for use in accessories.

Key Features

■ High performance stereo DAC to headphone ■ Flexible digital mixing from all seven inputs to

playback path with 110 dB dynamic range

all six outputs with independent gain on each

■ 4 mW stereo playback power consumption

mixer path

■

DAC digital filters with audio and voice mode

options, five-band equalizer and five

■

Ability to run the ADCs at a different sample

rate to the DACs on a single I2S interface

programmable biquad stages

■ Digital tone generator with built-in support for

■ Dedicated low-latency digital sideband filter

DTMF

with three programmable biquad stages

■ System controller for simplified, pop-free start-

■ High performance microphone to ADC record up and shutdown

path with 105 dB dynamic range

■ Phase-locked loop with sample rate tracking

■ 2.5 mW stereo record power consumption

supporting MCLK frequencies from 2 MHz to

■

ADC digital filters with audio and voice mode

options

■

54 MHz

Automatic tuning of on-chip reference

■ 500 µW always-on record mode with

oscillator for clock-free operation in low-power

modes

■

automatic level detection

Hybrid analog / digital automatic level control

■

4-wire digital audio interface with support for

I2S, four-channel I2S, TDM and other audio

to dynamically control the record level

formats

■ Shutdown mode offering current consumption ■ 2-wire I2C compatible control interface with

during standby of 2.5 µA

support for High Speed mode up to 3.4 MHz

■ Two low-noise microphone bias regulators ■ 24-bit data at up to 96 kHz sample rate

with programmable output voltage and ultra-

low power mode

■

The headphone amplifier can be run directly

■ A high efficiency two-level, true-ground charge

from the supply, thus eliminating the need for

charge pump capacitors

pump for generating class-G headphone

supplies

■ Voice mode filtering up to 32 kHz

Applications

■ Hearables

■ Wireless and wired headphones

■ Wireless and wired headsets

Datasheet

CFR0011-120-00

Revision 2.5

1 of 171

01 Sep 2016

© 2016 Dialog Semiconductor

1 page

DA7217

Ultra-Low Power Stereo Codec

9.4.1 Digital to Analog Converter.................................................................................. 53

9.4.2 Headphone Amplifiers ......................................................................................... 53

9.4.3 Charge Pump Control .......................................................................................... 56

9.4.3.1 Charge Pump Initial and Switching Current .................................... 57

9.4.4 Tracking the Demands on the Charge Pump Output .......................................... 57

9.4.4.1 cp_mchange = 00 (Manual Mode)................................................... 57

9.4.4.2 cp_mchange = 01 (Tracking the PGA Gain Setting) ....................... 57

9.4.4.3 cp_mchange = 10 (Tracking the DAC Signal Setting)..................... 57

9.4.4.4 cp_mchange = 11 (Tracking the Output Signal Magnitude) ............ 58

9.4.5

Specifying Clock Frequencies when Tracking the Charge Pump Output

Demand ............................................................................................................... 59

9.4.6 Other Charge Pump Controls .............................................................................. 59

9.4.7 True-Ground Supply Mode .................................................................................. 59

9.5 Phase Locked Loop ............................................................................................................ 59

9.5.1 PLL Bypass Mode................................................................................................ 59

9.5.2 Normal PLL Mode (DAI Master) .......................................................................... 60

9.5.3 Example Calculation of the Feedback Divider Setting: ....................................... 61

9.5.4 Sample Rate Matching PLL Mode (DAI Slave) ................................................... 61

9.5.5 MCLK Input .......................................................................................................... 62

9.5.5.1 MCLK Detection............................................................................... 62

9.5.6 Audio Reference Oscillator .................................................................................. 62

9.5.6.1 Oscillator Calibration........................................................................ 62

9.5.6.2 Procedure for Calibrating the Reference Oscillator......................... 63

9.5.7 Internal System Clock.......................................................................................... 63

9.6 Reference Generation......................................................................................................... 63

9.6.1 Voltage References ............................................................................................. 63

9.6.2 Bias Currents ....................................................................................................... 63

9.6.3 Voltage Levels ..................................................................................................... 63

9.6.3.1 Digital Regulator .............................................................................. 63

9.6.3.2 Digital Input/Output Pins Voltage Level ........................................... 64

9.7 I2C Control Interface............................................................................................................ 64

9.8 Digital Audio Interface ......................................................................................................... 67

9.8.1 DAI Channels....................................................................................................... 68

9.8.2 DAI WCLK Tristate Mode .................................................................................... 69

9.9 Interrupt Control .................................................................................................................. 69

9.9.1 Level Detect Events............................................................................................. 69

9.10 System Settings .................................................................................................................. 70

9.10.1 Sample Rate ........................................................................................................ 70

9.10.2 Gain Ramp Rate .................................................................................................. 70

9.10.3 Program Counter Control..................................................................................... 70

9.10.4 Soft Reset ............................................................................................................ 70

10 Register Maps and Definitions................................................................................................... 71

11 Package Information ................................................................................................................. 157

12 External Components ............................................................................................................... 158

13 Ordering Information ................................................................................................................ 158

Appendix A Applications Information ........................................................................................... 159

Datasheet

CFR0011-120-00

Revision 2.5

5 of 171

01 Sep 2016

© 2016 Dialog Semiconductor

5 Page

DA7217

Ultra-Low Power Stereo Codec

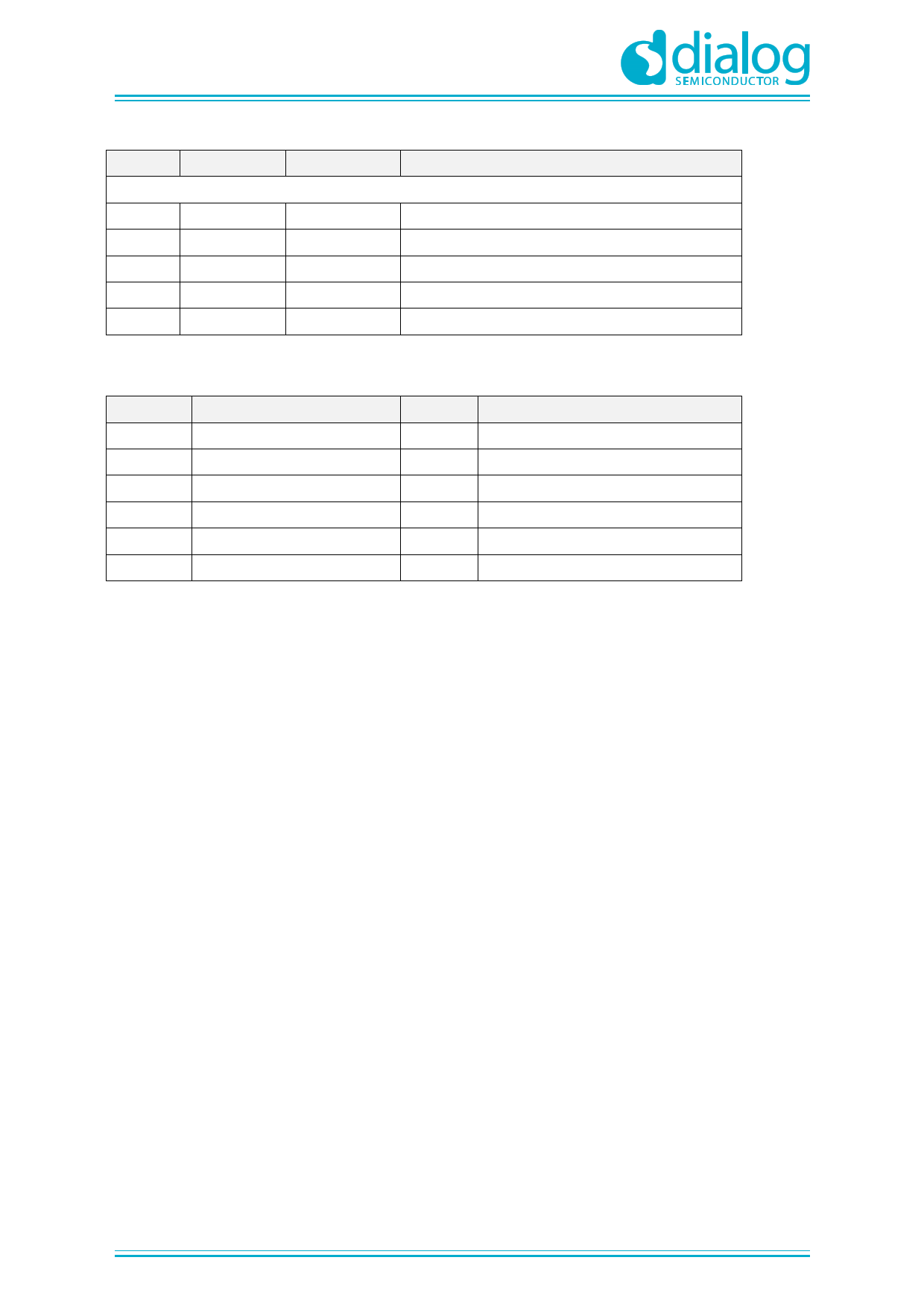

Pin No. Pin Name

Supplies

B8 VDD

A13 VDD_MIC

C5 VDD_IO

B2 GND_CP

B10 GND

Type (Table 2) Description

AI Main analog supply

AI Supply for MICBIAS LDO

AI Supply for digital interface and LDO

AI Ground reference

AI Ground reference

Table 2: Pin Type Definition

Pin Type Description

Pin Type Description

DI Digital Input

AI Analog Input

DO Digital Output

AO Analog Output

DIO Digital Input/Output

AIO Analog Input/Output

DIOD

Digital Input/Output open drain SPU

Switchable pull-up resistor

PU Fixed pull-up resistor

SPD

Switchable pull-down resistor

PD Fixed pull-down resistor

4.1 Input Pins

4.1.1 MIC1_P (DMIC1CLK)

MIC1_P is the positive differential input for the first analog microphone channel. It can be used as a

single-ended input (see Figure 8).

Alternatively for digital microphones, MIC1_P is used to provide a clock output.

4.1.2 MIC1_N (DMIC1IN)

MIC1_N is the negative differential input for the first analog microphone channel. It can be used as a

single-ended input.

Alternatively for digital microphones and active noise cancelling (ANC) applications, MIC1_N is used

as a pulse density modulated (PDM) data input.

4.1.3 MIC2_P (DMIC2CLK)

MIC2_P is the positive differential input for the second analog microphone channel. It can be used as

a single-ended input.

Alternatively for digital microphones, MIC2_P is used to provide a clock output.

4.1.4 MIC2_N (DMIC2IN)

MIC2_N is the negative differential input for the second analog microphone channel. It can be used

as a single-ended input.

Alternatively for digital microphones and ANC applications, MIC2_N is used as a PDM data input.

4.1.5 MCLK

MCLK is the master clock input pin. It is used as the main system clock either directly or via the PLL.

Datasheet

CFR0011-120-00

Revision 2.5

11 of 171

01 Sep 2016

© 2016 Dialog Semiconductor

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DA7217.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DA7210 | Ultra-low power stereo codec | Dialog Semiconductor |

| DA7211 | Ultra-low power stereo codec | Dialog Semiconductor |

| DA7212 | Ultra-low power stereo codec | Dialog Semiconductor |

| DA7217 | Ultra-Low Power Stereo Codec | Dialog Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |