|

|

PDF GS8182S09BGD Data sheet ( Hoja de datos )

| Número de pieza | GS8182S09BGD | |

| Descripción | 18Mb Burst of 2 SigmaSIO DDR-II SRAM | |

| Fabricantes | GSI Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GS8182S09BGD (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

GS8182S08/09/18/36BD-400/375/333/300/250/200/167

165-Bump BGA

Commercial Temp

Industrial Temp

18Mb Burst of 2

SigmaSIO DDR-IITM SRAM

400 MHz–167 MHz

1.8 V VDD

1.8 V and 1.5 V I/O

Features

• Simultaneous Read and Write SigmaSIO™ Interface

• JEDEC-standard pinout and package

• Dual Double Data Rate interface

• Byte Write controls sampled at data-in time

• DLL circuitry for wide output data valid window and future

frequency scaling

• Burst of 2 Read and Write

• 1.8 V +100/–100 mV core power supply

• 1.5 V or 1.8 V HSTL Interface

• Pipelined read operation

• Fully coherent read and write pipelines

• ZQ mode pin for programmable output drive strength

• IEEE 1149.1 JTAG-compliant Boundary Scan

• Pin-compatible with present 9Mb, 36Mb, and 72Mb and

future 144Mb devices

• 165-bump, 13 mm x 15 mm, 1 mm bump pitch BGA package

• RoHS-compliant 165-bump BGA package available

SigmaSIO DDR-II™ Family Overview

GS8182S08/09/18/36BD are built in compliance with the

SigmaSIO DDR-II SRAM pinout standard for Separate I/O

synchronous SRAMs. They are 18,874,368-bit (18Mb)

SRAMs. These are the first in a family of wide, very low

voltage HSTL I/O SRAMs designed to operate at the speeds

needed to implement economical high performance

networking systems.

Clocking and Addressing Schemes

A Burst of 2 SigmaSIO DDR-II SRAM is a synchronous

device. It employs dual input register clock inputs, K and K.

The device also allows the user to manipulate the output

register clock input quasi independently with dual output

register clock inputs, C and C. If the C clocks are tied high, the

Bottom View

165-Bump, 13 mm x 15 mm BGA

1 mm Bump Pitch, 11 x 15 Bump Array

JEDEC Std. MO-216, Variation CAB-1

K clocks are routed internally to fire the output registers

instead. Each Burst of 2 SigmaSIO DDR-II SRAM also

supplies Echo Clock outputs, CQ and CQ, which are

synchronized with read data output. When used in a source

synchronous clocking scheme, the Echo Clock outputs can be

used to fire input registers at the data’s destination.

Each internal read and write operation in a SigmaSIO DDR-II

B2 RAM is two times wider than the device I/O bus. An input

data bus de-multiplexer is used to accumulate incoming data

before it is simultaneously written to the memory array. An

output data multiplexer is used to capture the data produced

from a single memory array read and then route it to the

appropriate output drivers as needed. Therefore, the address

field of a SigmaSIO DDR-II B2 is always one address pin less

than the advertised index depth (e.g., the 2M x 8 has a 1M

addressable index).

Parameter Synopsis

tKHKH

tKHQV

-400

2.5 ns

0.45 ns

-375

2.67 ns

0.45 ns

-333

3.0 ns

0.45 ns

-300

3.3 ns

0.45 ns

-250

4.0 ns

0.45 ns

-200

5.0 ns

0.45 ns

-167

6.0 ns

0.5 ns

Rev: 1.03c 11/2011

1/36

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2007, GSI Technology

1 page

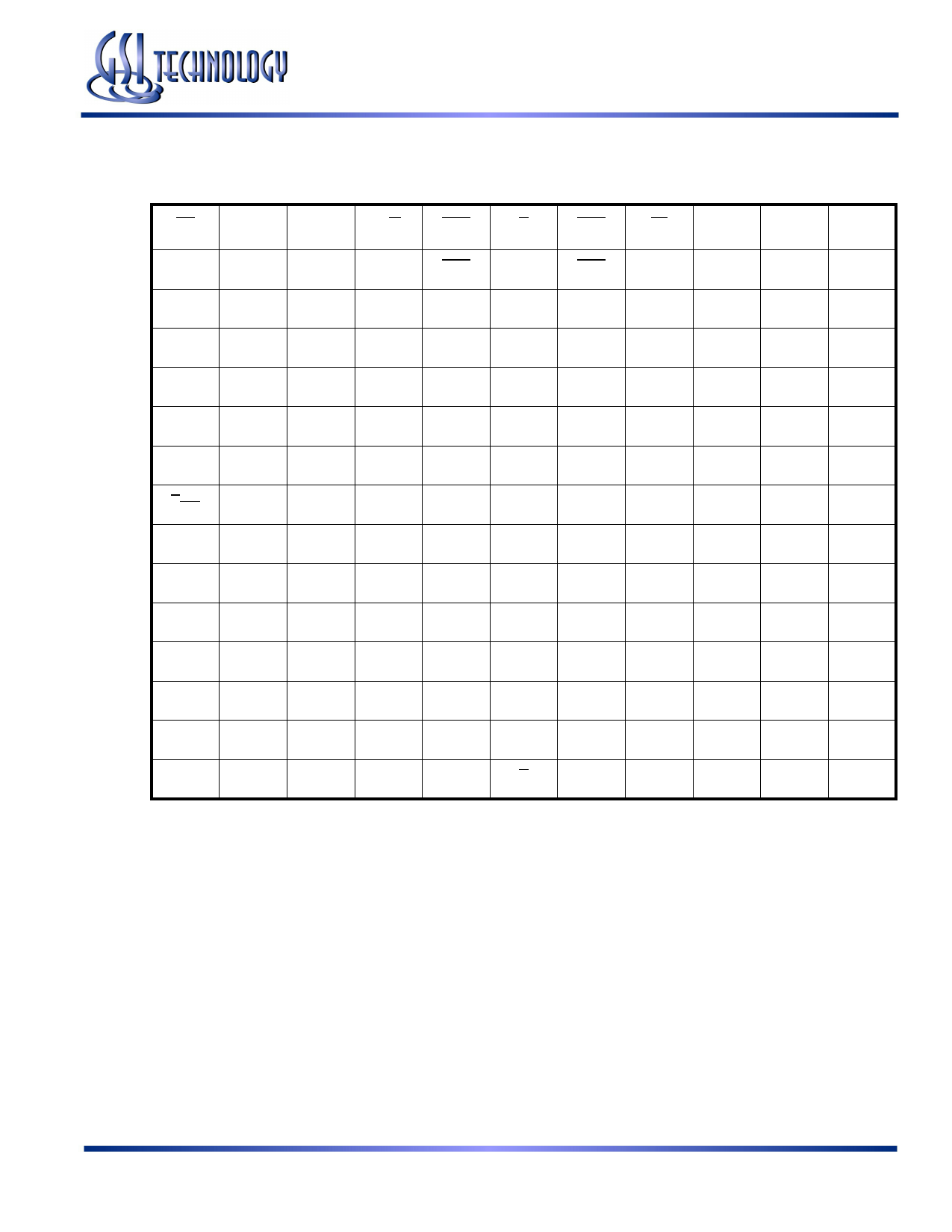

GS8182S08/09/18/36BD-400/375/333/300/250/200/167

512K x 36 SigmaQuad SRAM—Top View

1 2 3 4 5 6 7 8 9 10 11

A

CQ

NC/SA NC/SA

(288Mb) (72Mb)

R/W

BW2

K

BW1

LD

NC/SA NC/SA

(36Mb) (144Mb)

CQ

B Q27 Q18 D18 SA BW3 K BW0 SA D17 Q17 Q8

C D27 Q28 D19 VSS SA SA SA VSS D16 Q7 D8

D D28 D20 Q19 VSS VSS VSS VSS VSS Q16 D15 D7

E

Q29

D29

Q20

VDDQ

VSS

VSS

VSS

VDDQ

Q15

D6

Q6

F

Q30 Q21 D21

VDDQ

VDD

VSS

VDD

VDDQ

D14

Q14

Q5

G

D30 D22 Q22 VDDQ VDD

VSS

VDD

VDDQ

Q13

D13

D5

H

DOFF

VREF

VDDQ

VDDQ

VDD

VSS

VDD

VDDQ

VDDQ

VREF

ZQ

J

D31

Q31

D23

VDDQ

VDD

VSS

VDD

VDDQ

D12

Q4

D4

K

Q32 D32 Q23 VDDQ VDD

VSS

VDD

VDDQ

Q12

D3

Q3

L

Q33

Q24

D24

VDDQ

VSS

VSS

VSS

VDDQ

D11

Q11

Q2

M D33 Q34 D25 VSS VSS VSS VSS VSS D10 Q1 D2

N

D34 D26 Q25 VSS SA

SA

SA

VSS Q10

D9

D1

P

Q35 D35 Q26

SA

SA

C

SA SA Q9 D0 Q0

R

TDO TCK

SA

SA

SA

C

SA SA SA TMS TDI

11 x 15 Bump BGA—15 x 17 mm2 Body—1 mm Bump Pitch

Rev: 1.03c 11/2011

5/36

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2007, GSI Technology

5 Page

K

K

Address

LD Bank 1

LD Bank 2

R/W Bank 1

R/W Bank 2

BWx Bank 1

BWx Bank 2

D Bank 1

D Bank 2

C Bank 1

C Bank 1

Q Bank 1

CQ Bank 1

CQ Bank 1

C Bank 2

C Bank 2

Q Bank 2

CQ Bank 2

CQ Bank 2

Write B

GS8182S08/09/18/36BD-400/375/333/300/250/200/167

Burst of 2 SigmaSIO DDR-II SRAM Depth Expansion

Read C

Write D

Read E

Write F

Read G

Read H

Read J

NOP

BCDE FGH J

B+1

B

D+1

D

F+1

F

E E+1

H H+1

C C+1

G G+1

J

Rev: 1.03c 11/2011

11/36

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2007, GSI Technology

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet GS8182S09BGD.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GS8182S09BGD | 18Mb Burst of 2 SigmaSIO DDR-II SRAM | GSI Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |