|

|

PDF A29L001 Data sheet ( Hoja de datos )

| Número de pieza | A29L001 | |

| Descripción | Boot Sector Flash Memory | |

| Fabricantes | AMIC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A29L001 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

A29L001 Series

128K X 8 Bit CMOS 3.0 Volt-only,

Boot Sector Flash Memory

Document Title

128K X 8 Bit CMOS 3.0 Volt-only, Boot Sector Flash Memory

Revision History

Rev. No.

0.0

0.1

1.0

History

Initial issue

Change device ID to EDh (Top boot) and 6Dh (Bottom boot) on

Table 5.

Final version release

Issue Date

August 28, 2014

November 12, 2014

Remark

Preliminary

December 7, 2015

Final

(December, 2015, Version 1.0)

AMIC Technology, Corp.

AMIC reserves the right to change products and specifications discussed herein without notice.

1 page

A29L001 Series

Absolute Maximum Ratings*

Storage Temperature Plastic Packages ….. 0°C to +70°C

………………………………. for -U series: -40°C to +85°C

Ambient Temperature with Power Applied... 0°C to +70°C

……………………………… for -U series: -40°C to +85°C

Voltage with Respect to Ground

VCC (Note 1) ………………………………. -0.5V to +4.0V

A9 & OE (Note 2) ………………………….. -0.5 to +11.5V

All other pins (Note 1) ……………… -0.5V to VCC + 0.5V

Output Short Circuit Current (Note 3) ……………..200mA

Notes:

1. Minimum DC voltage on input or I/O pins is -0.5V.

During voltage transitions, inputs may undershoot

VSS to -2.0V for periods of up to 20ns. Maximum DC

voltage on output and I/O pins is VCC +0.5V. During

voltage transitions, outputs may overshoot to VCC

+1.5V for periods up to 20ns.

2. Minimum DC input voltage on A9 pins is -0.5V. During

voltage transitions, A9, OE and RESET may

overshoot VSS to -2.0V for periods of up to 20ns.

Maximum DC input voltage on A9 and OE is +11.5V

which may overshoot to 12.5V for periods up to 20ns.

3. No more than one output is shorted at a time.

Duration of the short circuit should not be greater than

one second.

*Comments

Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to this device.

These are stress ratings only. Functional operation of

this device at these or any other conditions above

those indicated in the operational sections of these

specification is not implied or intended. Exposure to

the absolute maximum rating conditions for extended

periods may affect device reliability.

Operating Ranges

Commercial Devices

Ambient Temperature (TA) ………………… 0°C to +70°C

Extended Range Devices

Ambient Temperature (TA) ……………… -40°C to +85°C

VCC Supply Voltages

VCC for 0°C ~ +70°C …………………….. +2.7V to +3.6V

VCC for -40°C ~ +85°C (-U series) ………+3.0V to +3.6V

Operating ranges define those limits between which the

functionally of the device is guaranteed.

Device Bus Operations

This section describes the requirements and use of the

device bus operations, which are initiated through the

internal command register. The command register itself

does not occupy any addressable memory location. The

register is composed of latches that store the commands,

along with the address and data information needed to

execute the command. The contents of the register serve

as inputs to the internal state machine. The state

machine outputs dictate the function of the device. The

appropriate device bus operations table lists the inputs

and control levels required, and the resulting output. The

following subsections describe each of these operations

in further detail.

Table 1. A29L001 Device Bus Operations

Operation

Read

Write

CMOS Standby

TTL Standby

Output Disable

Sector Protect (Note)

CE

L

L

VCC ± 0.3 V

H

L

L

OE

L

H

X

X

H

H

Sector Unprotect (Note)

LH

Temporary Sector Unprotect

(Note)

X

X

WE RESET

A0 – A16

I/O0 - I/O7

HH

AIN DOUT

LH

AIN DIN

X VCC ± 0.3 V

X

High-Z

X VCC ± 0.3 V

X

High-Z

HH

X High-Z

L VID Sector Address, DIN

A6=L, A1=H, A0=L

L VID Sector Address, DIN

A6=H, A1=H, A0=L

X VID

X

X

Legend:

L = Logic Low = VIL, H = Logic High = VIH, VID = 10.5 ± 1.0V, X = Don't Care, DIN = Data In, DOUT = Data Out, AIN = Address In

Note:

See the "Sector Protection/Unprotection" section and Temporary Sector Unprotect for more information.

(December, 2015, Version 1.0)

4 AMIC Technology, Corp.

5 Page

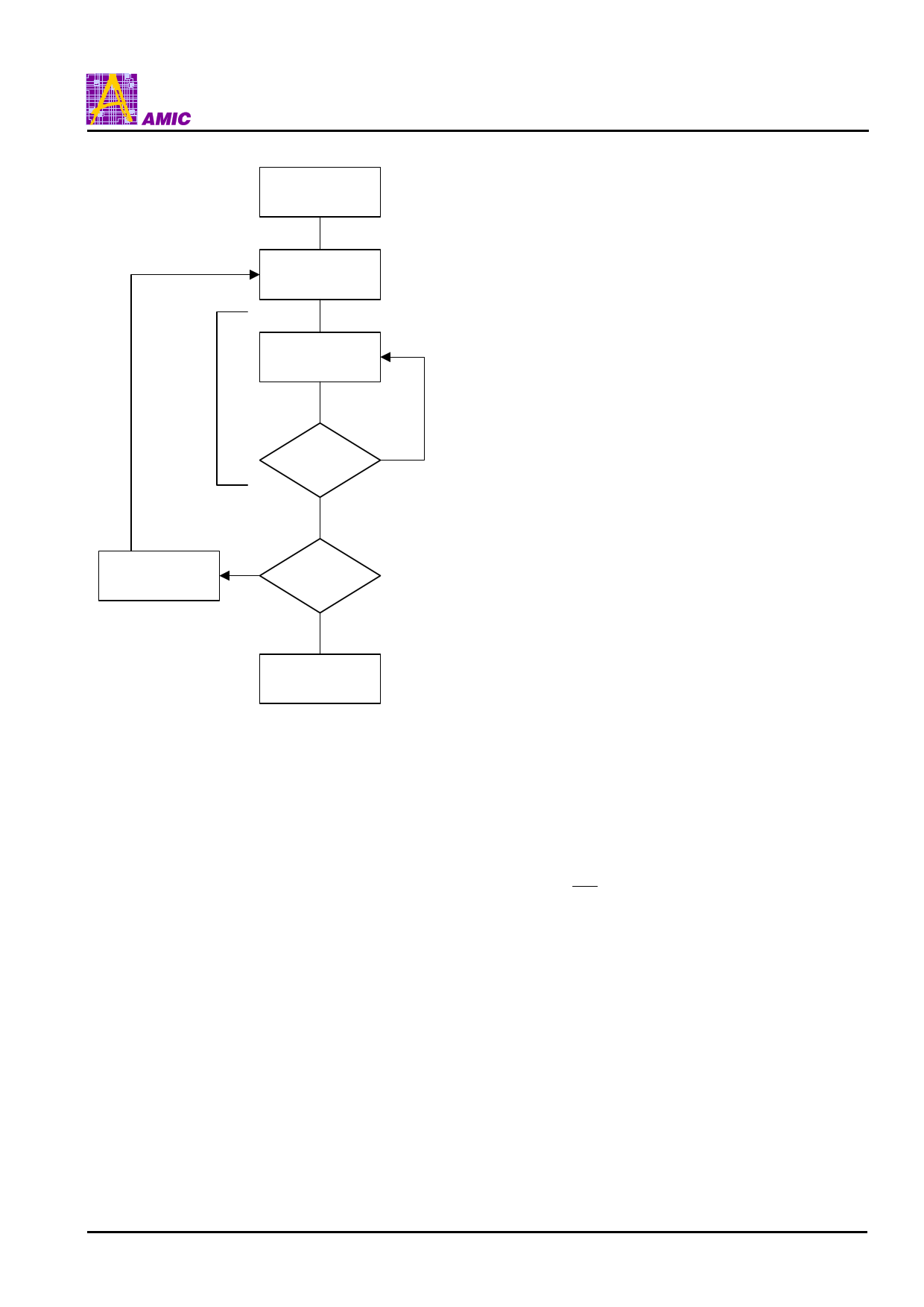

START

Embedded

Program

algorithm in

progress

Increment Address

Write Program

Command

Sequence

Data Poll

from System

Verify Data ?

Yes

No

Last Address ?

Yes

Programming

Completed

Note : See the appropriate Command Definitions table for

program command sequence.

Figure 3. Program Operation

Chip Erase Command Sequence

Chip erase is a six-bus-cycle operation. The chip erase

command sequence is initiated by writing two unlock

cycles, followed by a set-up command. Two additional

unlock write cycles are then followed by the chip erase

command, which in turn invokes the Embedded Erase

algorithm. The device does not require the system to

preprogram prior to erase. The Embedded Erase

algorithm automatically preprograms and verifies the

entire memory for an all zero data pattern prior to electrical

erase. The system is not required to provide any controls

or timings during these operations. The Command

Definitions table shows the address and data

requirements for the chip erase command sequence.

Any commands written to the chip during the Embedded

Erase algorithm are ignored.

The system can determine the status of the erase

operation by using I/O7, I/O6, or I/O2. See "Write Operation

Status" for information on these status bits.

A29L001 Series

When the Embedded Erase algorithm is complete, the

device returns to reading array data and addresses are no

longer latched.

Figure 4 illustrates the algorithm for the erase operation.

See the Erase/Program Operations tables in "AC

Characteristics" for parameters, and to the Chip/Sector

Erase Operation Timings for timing waveforms.

Sector Erase Command Sequence

Sector erase is a six-bus-cycle operation. The sector

erase command sequence is initiated by writing two

unlock cycles, followed by a set-up command. Two

additional unlock write cycles are then followed by the

address of the sector to be erased, and the sector erase

command. The Command Definitions table shows the

address and data requirements for the sector erase

command sequence.

The device does not require the system to preprogram the

memory prior to erase. The Embedded Erase algorithm

automatically programs and verifies the sector for an all

zero data pattern prior to electrical erase. The system is

not required to provide any controls or timings during

these operations.

After the command sequence is written, a sector erase

time-out of 50μs begins. During the time-out period,

additional sector addresses and sector erase commands

may be written. Loading the sector erase buffer may be

done in any sequence, and the number of sectors may be

from one sector to all sectors. The time between these

additional cycles must be less than 50μs, otherwise the

last address and command might not be accepted, and

erasure may begin. It is recommended that processor

interrupts be disabled during this time to ensure all

commands are accepted. The interrupts can be re-

enabled after the last Sector Erase command is written. If

the time between additional sector erase commands can

be assumed to be less than 50μs, the system need not

monitor I/O3. Any command other than Sector Erase or

Erase Suspend during the time-out period resets the

device to reading array data. The system must rewrite the

command sequence and any additional sector addresses

and commands.

The system can monitor I/O3 to determine if the sector

erase timer has timed out. (See the " I/O3: Sector Erase

Timer" section.) The time-out begins from the rising edge

of the final WE pulse in the command sequence.

Once the sector erase operation has begun, only the

Erase Suspend command is valid. All other commands are

ignored.

When the Embedded Erase algorithm is complete, the

device returns to reading array data and addresses are no

longer latched. The system can determine the status of

the erase operation by using I/O7, I/O6, or I/O2. Refer to

"Write Operation Status" for information on these status

bits. Figure 4 illustrates the algorithm for the erase

operation. Refer to the Erase/Program Operations tables

in the "AC Characteristics" section for parameters, and to

the Sector Erase Operations Timing diagram for timing

waveforms.

(December, 2015, Version 1.0)

10 AMIC Technology, Corp.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A29L001.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A29L001 | Boot Sector Flash Memory | AMIC |

| A29L004 | 512K X 8 Bit CMOS 3.0 Volt-only/ Boot Sector Flash Memory | AMIC Technology |

| A29L004A | Boot Sector Flash Memory | AMIC Technology |

| A29L004L | 512K X 8 Bit CMOS 3.0 Volt-only/ Boot Sector Flash Memory | AMIC Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |