|

|

PDF CDP1020 Data sheet ( Hoja de datos )

| Número de pieza | CDP1020 | |

| Descripción | SMBus/I2C ACPI Dual Device Bay Controller | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CDP1020 (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

CDP1020

Data Sheet

April 1999

File Number 4704

SMBus/I2C ACPI Dual Device Bay

Controller

The CDP1020 is an ACPI compliant Device Bay Controller

(DBC) that can control two device bays. The controller

interfaces to the host system through the industry standard

I2C or System Management Bus (SMBus) and is fully

compliant with Device Bay Specification 0.90. The CDP1020

is designed to be compatible with the integrated SMBus host

controller of the PiiX4/PiiX6 in Intel Architecture platforms.

The CDP1020 is designed to be placed on the host

motherboard, on a riser, or adjacent to the Device Bay

connectors. The required clock source is generated from an

internal oscillator on the CLK pin, with an external RC to set

the frequency. This lowers the system cost and allows the

CDP1020 to remain active during S3-S5 system states

where all clock generators have been stopped.

One of the key features of this device is the on-chip level

shifters that provide slew rate controlled, direct gate drive for

external N-Channel MOSFETs (Intersil HUF76113DK8

recommended) to switch the device bay VID supplies.

Switching an N-Channel device as opposed to a P-Channel

reduces both device cost and device count, resulting in an

overall lower system cost.

Configuration data for the CDP1020, including subsystem

vendor ID, subsystem revision, bay size and device bay

capabilities are designed to be written into the CDP1020 by

the system BIOS at power up. The registers for this data are

write-once-only and thus become read-only after the initial

BIOS write.

The address selection pins (AD1 and AD0) allow the

CDP1020 to occupy any one of four I2C/SMBus addresses.

This enables up to four CDP1020 devices to coexist in a

system.

The CDP1020 implements high current outputs for direct

drive (with a limiting resistor) of the optional bay status

LEDs. These indicators are two color (green/amber)

common anode or anti-parallel LEDs that indicate the device

bay status per the Device Bay Specification 0.90.

Ordering Information

PART

NUMBER

TEMP. RANGE

(oC) PACKAGE

CDP1020

0 to 85

28 Ld SOIC

PKG. NO.

M28.3

For More Information Contact:

Mike Coletta (714) 433-0600

Terry Pierce (407) 729-5835

Features

• Fully Compliant with Device Bay Specification 0.90 and

ACPI Specification 1.0

• Industry Standard SMBus/I2C Interface

• Controls for Two Device Bays

• Onboard Level Shifting for Direct Drive of N-Channel

MOSFET VID Switches

• Integrated Pull-up Resistors on 1394PRx, USBPRx,

SECUREx, and REMREQx Inputs

• RC Type Oscillator - Low Cost and Low Power

Consumption

• Operational Voltage from 3.3 to 5.5V

• “5V Tolerant” Inputs at all Operating Voltages

• Write-Once BIOS/External Configuration

• Removal Request Input for Each Bay

• Security Lock Input for Each Bay

• High Current Device Bay LED Indicator Drivers With

Separate High-Side Power Input

• Configurable Level/Pulse Bay Solenoid Drivers

• Programmable Insertion Time Out Delay

• HCMOS Technology; 28 Lead Plastic SOIC

Pinout

CDP1020 (SOIC)

TOP VIEW

RESET 1

TEST (VDD) 2

1394PR0 3

USBPR0 4

REMREQ0 5

SECURE0 6

1394PR1 7

USBPR1 8

REMREQ1 9

SECURE1 10

SDA 11

SCK 12

ALRT 13

VGATE 14

28 AD1

27 AD0

26 CLK

25 VSS

24 VDD

23 VLED

22 LEDA1

21 LEDG1

20 LEDA0

19 LEDG0

18 SFTLOCK1

17 SFTLOCK0

16 PWREN1

15 PWREN0

2-418

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

1 page

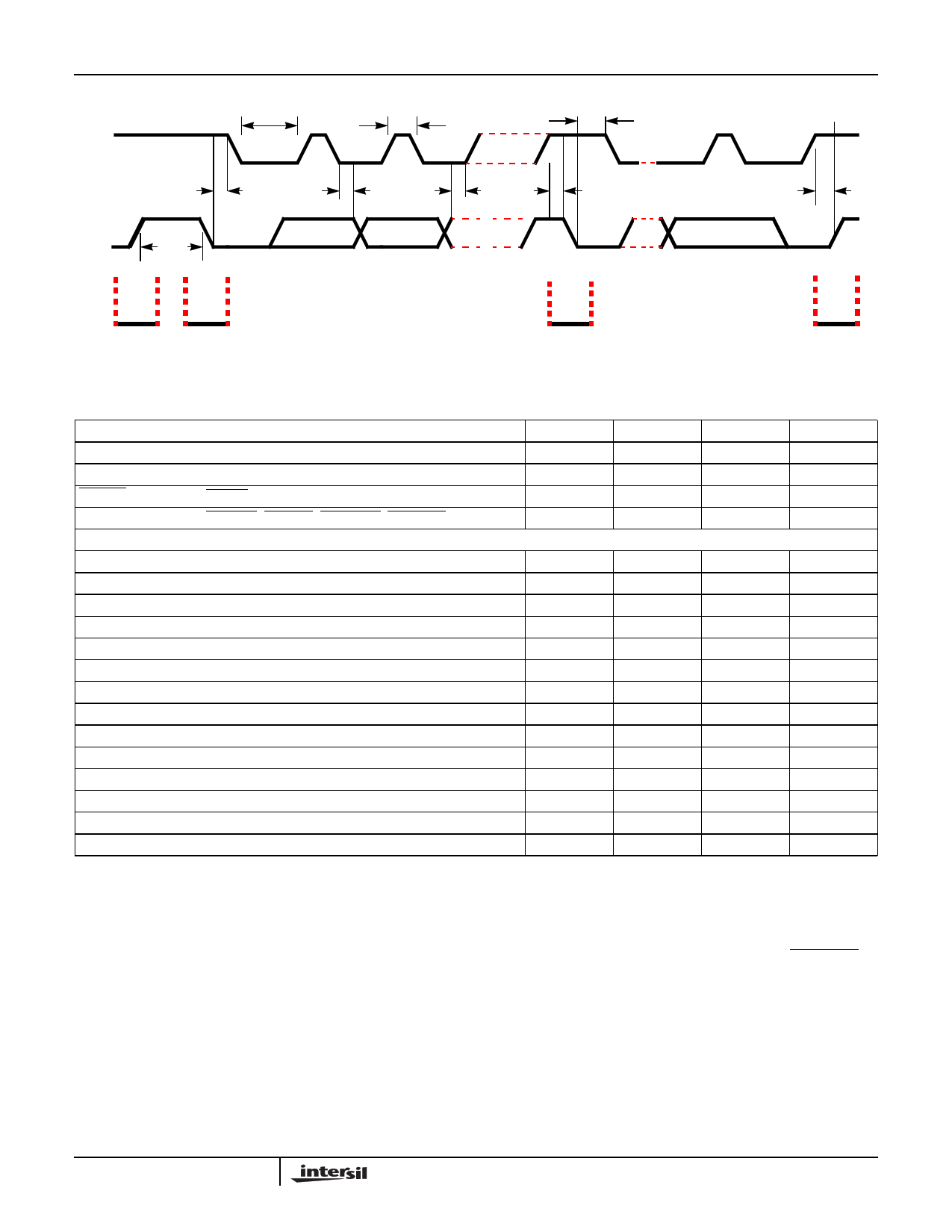

CDP1020

SCK

SDA

tLOW

tHD:STA

tBUF

tHIGH

tHD:DAT

tSU:DAT

tHD:STA

tSU:STA

tSU:STO

STOP

START

STOP

FIGURE 1. CONTROL TIMING

START

Control Timing VDD = 3.3V ±10%, TA = 0oC to 85oC

PARAMETER

Frequency Of Operation (4.0MHz nominal) (CLK Pin)

Suspend Recovery Start-up Time

RESET Pulse Width (RESET Pin)

Input Debounce Time (1394PRx, USBPRx, REMREQx, SECUREx Pins)

SMBus SCK and SDA Pins

SCK Frequency

SMBus Free Time

Hold Time After (Repeated) Start Condition

Repeated Start Condition Setup Time

Stop Condition Setup Time

Data Hold Time

Data Setup Time

SCK Time-out Period

SCK Low Period

SCK High Period

Slave SCK Extend Period (cumulative)

Master SCK Extend Period (cumulative)

SCK/SMBDAT Fall Time

SCK/SMBDAT Rise Time

Notational Conventions

The following conventions are used throughout this

document:

• Hexadecimal numbers are denoted with a “$” symbol

preceding the number.

• Binary numbers are represented with a “%” symbol

proceeding the number, or a “b” following.

• Because of the large mix of active-low and active-high

signals used in connection with the CDP1020, the terms

“asserted” and “de-asserted” will be used exclusively. An

active low signal is asserted when it is at a logic 0 and de-

asserted when it is at a logic 1 state. Conversely, an active

high signal is at a logic 1 state when asserted and at a

logic 0 state when de-asserted. The terms reset, clear,

SYMBOL

fCLK

tRSUS

tRL

tDB

fSMB

tBUF

tHD:STA

tSU:STA

tSU:STO

tHD:DAT

tSU:DAT

tTIMEOUT

tLOW

tHIGH

tLOW:SEXT

tLOW:MEXT

tF

tR

MIN

2.0

0.9

6

50

10

4.7

4.0

4.7

4.0

300

250

25

4.7

4.0

-

-

-

-

MAX

4.5

1

-

-

100

-

-

-

-

-

-

35

-

50

25

10

300

1000

UNITS

MHz

ms

tOSC

ms

kHz

µs

µs

µs

µs

ns

ns

ms

µs

µs

ms

ms

ns

ns

and “low” can also mean logic 0; set or “high” can also

mean logic 1.

• Active low signals are represented with an overline; active

high signals have no overline. For example, REMREQ0 is

active low, PWREN0 is active high.

• There are many pins, signals, registers, and software bits

common to both Bay 0 and Bay 1; these names may

include the Bay number suffix (0 or 1), an “x” to represent

either, or no suffix at all. For example, PWREN, PWREN0,

or PWRENx may each be used to describe output pin(s).

2-422

5 Page

CDP1020

NOTE: The register set in the CDP1020 is implemented in little-

endian format, as specified in Device Bay Specification 0.90. As

such, the least significant byte in any register is in the lowest memory

address for that register; likewise the most significant byte is in the

highest memory address. In the DBCCR, for example, the least

significant byte (containing the configuration data) is at address $0C.

The most significant byte (containing all 0’s) is at address $0F.

The following subsections describe each of the registers

within the CDP1020.

Vendor ID Register, $00

Per Device Bay Specification 0.90, the first register in the

CDP1020 register set is the Vendor ID register. The contents

of this register identify the manufacturer of the Device Bay

Controller. This register is a read-only register that contains

$1260, the 16-bit Intersil Corporation PCI SIG identification

number. This number is contained in the lower two bytes of

the register; the upper two bytes are always read as $0000.

Bits 31:16

$0000

Bits 15:0

$1260 (Intersil PCI-SIG ID) $00

Revision ID Register, $04

The Revision ID register contains the 8-bit device bay

controller manufacturer revision ID. This number is used to

identify a particular Device Bay controller from the

manufacturer specified in the Vendor ID register. The

Revision ID is a read-only register that contains the 8-bit

revision code for the CDP1020. This number is contained in

the lower byte of the register; the upper three bytes are

always read as $000000.

Bits 31:8

$000000

Bits 7:0

Revision ID $04

Subsystem Vendor ID Register, $08

The Subsystem Vendor ID Register is used to identify the

manufacturer of the device bay system that the CDP1020 is

installed in. This register is implemented as a write-once-

only register and is designed to be written by the system

BIOS immediately after either the power-on-reset, or

asserting the RESET pin, which enables a write to this

register. Once written, this register becomes read-only and

should contain the 16-bit subsystem manufacturer

identification number. This register and the Subsystem ID

register are the only 16-bit registers in the CDP1020.

Bits 15:0

Subsystem Vendor ID

$08

Subsystem ID Register, $0A

The Subsystem ID register contains a 16-bit subsystem

vendor defined ID number. Typically, this number would

define the device bay system revision or model number. Like

the Subsystem Vendor ID, this register is implemented as a

write-once-only register and is designed to be written by the

system BIOS immediately after either the power-on-reset, or

asserting the RESET pin, which enables a write to this

register. Once written, this register becomes read-only. This

register and the Subsystem Vendor ID register are the only

16-bit registers in the CDP1020.

Bits 15:0

Subsystem ID

$0A

Device Bay Controller Capabilities Register, $0C

The Device Bay Controller Capabilities Register (DBCCR) is

designed to allow the operating system to easily identify the

features of the Device Bay system controlled by the

CDP1020. This register contains five write-once-only bits,

defined below. These bits, like those in the Subsystem

Vendor ID Register, are designed to be written by the system

BIOS immediately after power-on. Once written, they

become read-only. The upper 27 bits of the DBCCR are

always read as 0 This register is set to $00000002 at reset

(two bays, no security locks).

Bits 31:5

$00000

Bit 4

SECLOCK

Bits 3:0

BAYCNT[3:0]

$0C

BITS 31:5

Reserved for future use. Always read as 0.

SECLOCK

The SECLOCK bit indicates the presence of an optional

physical security lock on at least one of the device bays

controlled by the CDP1020. If set, then at least one of the

device bays has the physical security lock, the state of which

is available in the bay status register BSTRx. If clear, no

physical security lock exists in the system. SECLOCK is

implemented as a write-once-only bit intended to be written

by the BIOS immediately after system power-on. Once

written to, this bit becomes read-only.

BAYCNT[3:0]

The four BAYCNT bits represent the number of bays

controlled by the CDP1020 in binary form. These bits, like the

SECLOCK bit, are implemented as a write-once-only bits

intended to be written by the BIOS immediately after system

power-on. Once written to, they become read-only. Since the

CDP1020 is a two bay controller, the only valid values that can

be written to the BAYCNT[3:0] bits are 0, 1 and 2. If the OS

tries to write any other value, the CDP1020 will write a value

of 2 (%0010) to this bit field.

2-428

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet CDP1020.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CDP1020 | SMBus/I2C ACPI Dual Device Bay Controller | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |