|

|

PDF CL-PS7500FE Data sheet ( Hoja de datos )

| Número de pieza | CL-PS7500FE | |

| Descripción | System-on-a Chip for Internet Appliance | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CL-PS7500FE (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

CL-PS7500FE

Advance Data Book

FEATURES

s Available in 56- and 40-MHz speed grades

s System-on-a-chip solution

— 32-bit ARM7 processor with MMU

— 4K unified cache

— FPU (floating point unit)

— Graphics controller drives CRT or LCD

— CD-quality sound audio controller

— DRAM controller

— ROM/Flash controller

— Three-channel DMA for video, cursor, and sound

— PC-style I/O bus

— Two-state power management

— Eight general-purpose I/O lines

s Performance

— 50 Vax™-MIPS (Dhrystone®) at 56 MHz

— Up to 12 Mflops, double-precision FP (LINPACK)

s FPU

— Implements ANSI/IEEE Std 754-1985

— Single, double, and extended precision

System-on-a Chip for

Internet Appliance

OVERVIEW

The Cirrus Logic CL-PS7500FE is designed to be

used in internet appliances such as the network

computer, smart-TV, intranet terminal, screen

phones, DVD players, and so on.

The massively integrated CL-PS7500FE offers a

complete system-on-a-chip solution that includes a

32-bit ARM CPU with cache and MMU, CRT and

LCD controller, memory controller, FPU, CD-quality

sound controller, interface to the Cirrus Logic DSP

device for 56K modem and speakerphone, and a

PC-type I/O bus. To handle streaming of audio and

video data on the Internet, the CL-PS7500FE

includes a double-precision FPU to accelerate

software codecs.

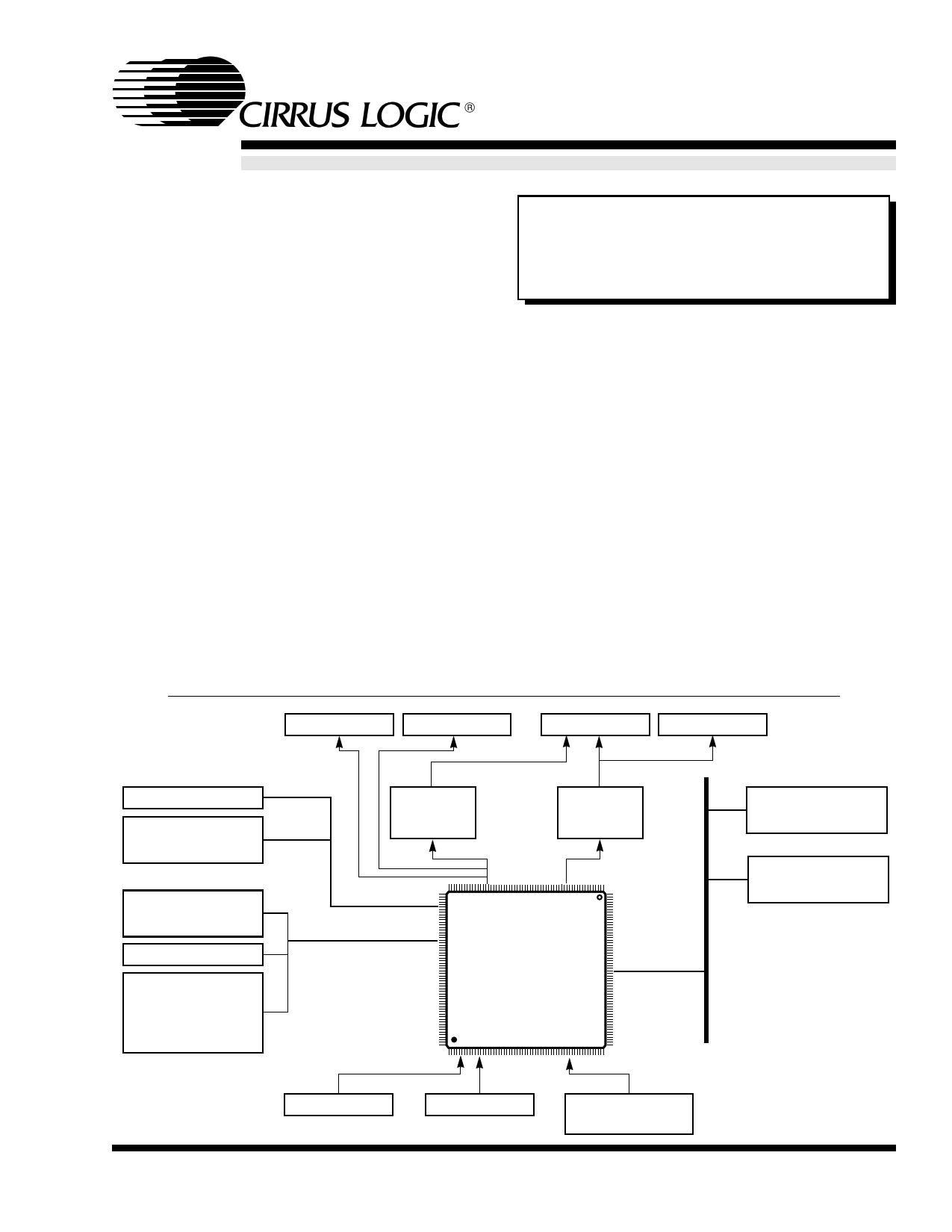

Functional

Block Diagram

(cont.)

COLOR LCD SVGA MONITOR

TV HEADPHONES

(cont.)

ROM

DRAM

(4 MBYTE, TYP)

ENCODER

PAL/NTSC

CD-DAC

CS4333

CONFIG. MEMORY

(NON-VOL.)

REALTIME CLOCK

FRONT PANEL:

STATUS LEDs

RUN/STANDBY SW

MEMORY BUS

VIDEO O/P

(RGB)

AUDIO O/P

(32 BIT)

I/O PORT

CL-PS7500FE

240-PIN PQFP

ISA-STYLE

BUS

2 ANALOG

2*PS/2 PORTS

INPUTS

www.DataSheet4U.com

KEYBOARD

MOUSE

GAMES DEVICE

(ANALOG)

Version 2.0

56k MODEM

CL-MD34XX

ETHERNET

CS89XX

June 1997

1 page

www.DataSheet4U.com

CL-PS7500FE

System-on-a-Chip for Internet Appliance

6. ARM PROCESSOR MMU .................................................................................................... 38

6.1 MMU Program-Accessible Registers................................................................................................38

6.1.1 Translation Table Base Register ......................................................................................39

6.1.2 Domain Access Control Register......................................................................................39

6.1.3 Fault Status Register ........................................................................................................39

6.1.4 Fault Address Register .....................................................................................................39

6.2 Address Translation ..........................................................................................................................39

6.3 Translation Process ..........................................................................................................................40

6.3.1 TTB (Translation Table Base)............................................................................................40

6.3.2 Level One Fetch................................................................................................................40

6.3.3 Level One Descriptor ........................................................................................................41

6.3.4 Page Table Descriptor.......................................................................................................41

6.3.5 Section Descriptor ............................................................................................................42

6.4 Translating Section References ........................................................................................................42

6.4.1 Level Two Descriptor.........................................................................................................42

6.5 Translating Small Page References..................................................................................................44

6.6 Translating Large Page References .................................................................................................45

6.7 MMU Faults and CPU Aborts ...........................................................................................................47

6.8 Fault Address and Fault Status Registers (FAR, FSR).....................................................................47

6.9 Domain Access Control ....................................................................................................................48

6.10 Fault-Checking Sequence ................................................................................................................48

6.10.1 Alignment Fault.................................................................................................................49

6.10.2 Translation Fault................................................................................................................50

6.10.3 Domain Fault ....................................................................................................................50

6.10.4 Permission Fault ...............................................................................................................50

6.11 External Aborts.................................................................................................................................50

6.11.1 Interaction of the MMU, IDC, and Write Buffer..................................................................51

7. REGISTER DESCRIPTIONS................................................................................................ 52

7.1 Register Configuration......................................................................................................................52

7.1.1 Big and Little Endian (the Bigend Bit) ...............................................................................52

7.1.2 Configuration Bits for Backward Compatibility ..................................................................53

7.2 Operating Mode Selection ................................................................................................................54

7.3 Registers ..........................................................................................................................................55

7.3.1 PSRs (Program Status Registers) ....................................................................................56

7.4 Exceptions ........................................................................................................................................57

7.4.1 FIQ....................................................................................................................................57

7.4.2 IRQ ...................................................................................................................................58

7.4.3 Abort .................................................................................................................................58

7.4.4 Software Interrupt .............................................................................................................59

7.4.5 Undefined Instruction Trap ................................................................................................60

7.4.6 Vector Summary ...............................................................................................................60

7.4.7 Exception Priorities...........................................................................................................61

7.4.8 Interrupt Latencies............................................................................................................61

7.4.9 Reset ................................................................................................................................61

7.5 Configuration Control Registers .......................................................................................................62

7.5.1 Backward Compatibility ....................................................................................................62

7.5.2 Internal Coprocessor Instructions.....................................................................................62

www.Da7.t5a.3SheeRt4egUis.tceorsm.......................................................................................................................... 63

7.6 Register 1: Control (Write only) ........................................................................................................64

4

TABLE OF CONTENTS

ADVANCE DATA BOOK v2.0

June 1997

5 Page

www.DataSheet4U.com

CL-PS7500FE

System-on-a-Chip for Internet Appliance

20. BUS INTERFACE................................................................................................................ 187

20.1 Bus Arbitration ................................................................................................................................187

20.2 Bus Cycle Types .............................................................................................................................187

20.3 Video DMA Bandwidth....................................................................................................................188

20.4 Video DMA Latency........................................................................................................................188

21. CLOCKS, POWER SAVING, AND RESET........................................................................ 191

21.1 Clock Control ..................................................................................................................................191

21.1.1 Video and Sound Subsystem Clocks..............................................................................191

21.1.2 I/O Clock Outputs ...........................................................................................................191

21.1.3 Synchronous/Asynchronous Mode for the ARM Processor............................................191

21.1.4 Clock Prescalars.............................................................................................................192

21.1.5 Clocking Schemes ..........................................................................................................192

21.2 Power Management........................................................................................................................192

21.2.1 SUSPEND Mode ............................................................................................................193

21.2.2 STOP Mode ....................................................................................................................194

21.3 Reset ..............................................................................................................................................195

22. ELECTRICAL SPECIFICATIONS ...................................................................................... 196

22.1 Absolute Maximum Ratings............................................................................................................196

22.2 DC Specifications ...........................................................................................................................197

22.2.1 DC Specifications — Digital Values ................................................................................197

22.3 Derating ..........................................................................................................................................198

22.4 AC Parameters — List of Timing Figures .......................................................................................199

22.5 System Reset Timing .....................................................................................................................200

22.6 Memory Subsystems......................................................................................................................201

22.7 I/O Subsystems ..............................................................................................................................209

22.8 System Timing (Clocks)..................................................................................................................222

23. PACKAGE ........................................................................................................................... 225

23.1 240-Pin PQFP Package Example...................................................................................................225

24. ORDERING INFORMATION EXAMPLE............................................................................ 226

www.DataSheet4U.com

10

TABLE OF CONTENTS

ADVANCE DATA BOOK v2.0

June 1997

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CL-PS7500FE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CL-PS7500FE | System-on-a Chip for Internet Appliance | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |