|

|

PDF DS1543 Data sheet ( Hoja de datos )

| Número de pieza | DS1543 | |

| Descripción | 64k NV Timekeeping RAM | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS1543 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

www.dalsemi.com

FEATURES

Integrated NV SRAM, real time clock, crystal,

power-fail control circuit and lithium energy

source

Clock registers are accessed identical to the

static RAM. These registers are resident in the

sixteen top RAM locations

Totally nonvolatile with over 10 years of

operation in the absence of power

Precision Power-On Reset

Programmable Watchdog Timer and RTC

Alarm

BCD coded year, month, date, day, hours,

minutes, and seconds with automatic leap year

compensation valid up to the year 2100

Battery voltage level indicator flag

Power-fail write protection allows for ±10%

Vcc power supply tolerance

Lithium energy source is electrically

disconnected to retain freshness until power is

applied for the first time

ORDERING INFORMATION

DS1543-XXX

(5V)

-70 70 ns access

-100 100 ns access

*DS1543W-XXX

(3.3V)

-120 120 ns access

-150 150 ns access

PRELIMINARY

DS1543

64k NV Timekeeping RAM

PIN ASSIGNMENT

RST

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 VCC

27 WE

26 IRQ/FT

25 A8

24 A9

23 A11

22 OE

21 A10

20 CE

19 DQ7

18 DQ6

17 DQ5

16 DQ4

15 DQ3

28-Pin Encapsulated Package

(700 Mil Extended)

PIN DESCRIPTION

A0-A12

- Address Input

DQ0-DQ7 - Data Input/Outputs

IRQ \FT

- Interrupt, Frequency Test

Output (Open-Drain)

RST - Power-On Reset Output

(Open-Drain)

CE - Chip Enable

OE - Output Enable

WE

VCC

GND

NC

- Write Enable

- Power Supply Input

- Ground

- No Connection

1 of 17

081000

1 page

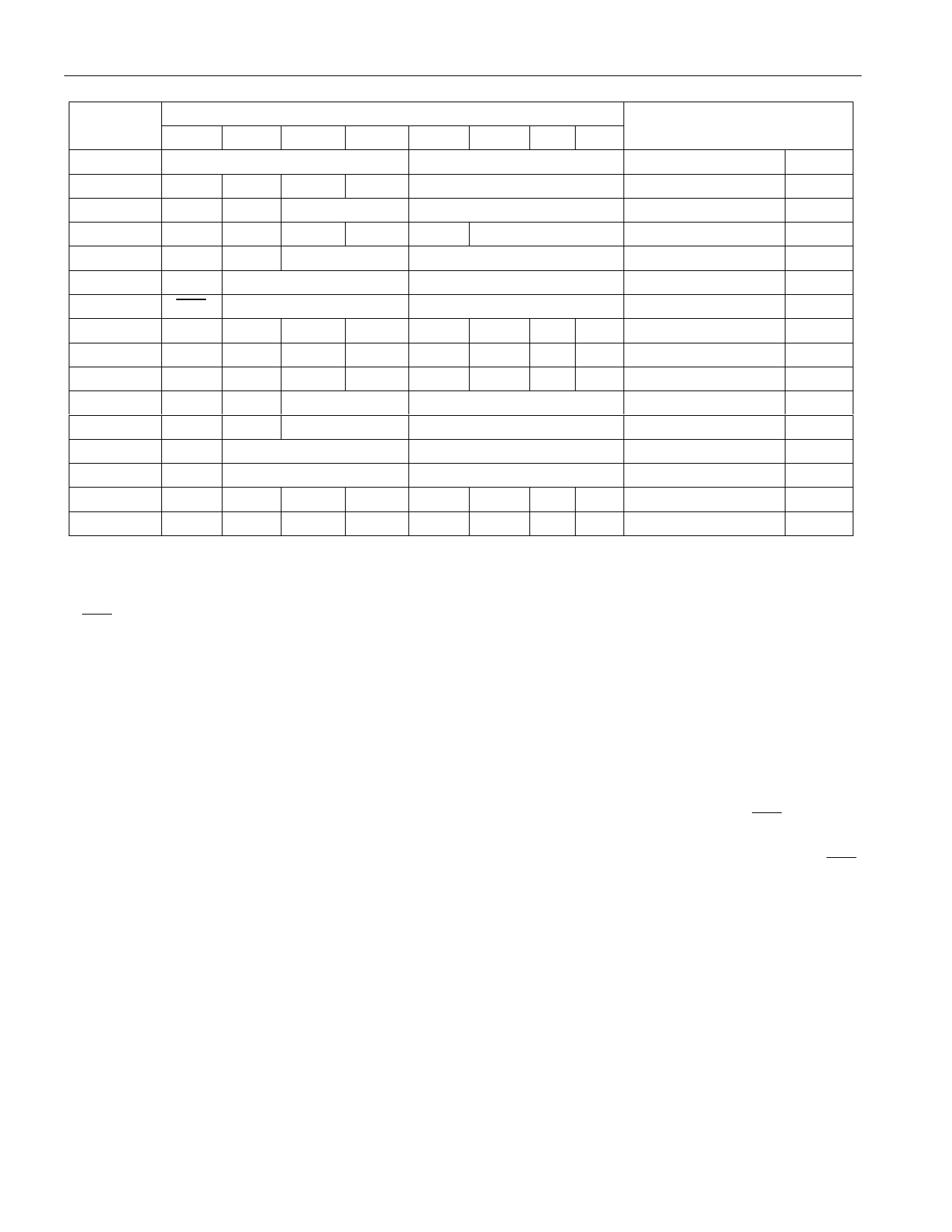

DS1543 REGISTER MAP Table 2

DATA

ADDRESS

B7 B6 B5 B4 B3

1FFFh

10 Year

1FFEh X X X 10 M

1FFDh X X

10 Date

1FFCh

X FT

X

X

X

1FFBh X X

10 HOUR

1FFAh

X

10 MINUTES

1FF9h

OSC

10 SECONDS

1FF8h W R Y Y Y

1FF7h WDS BMB4 BMB3 BMB2 BMB1

1FF6h AE Y ABE Y

Y

1FF5h AM4 Y

10 DATE

1FF4h AM3 Y

10 HOURS

1FF3h AM2

10 MINUTES

1FF2h AM1

10 SECONDS

1FF1h Y Y Y Y Y

1FF0h

WF AF

0

BLF 0

B2 B1

YEAR

MONTH

DATE

DAY

HOUR

MINUTES

SECONDS

YY

BMB0 RB1

YY

DATE

HOURS

MINUTES

SECONDS

YY

00

B0

Y

RB0

Y

Y

0

DS1543

FUNCTION/RANGE

YEAR

MONTH

DATE

DAY

HOUR

MINUTES

SECONDS

CONTROL

WATCHDOG

INTERRUPTS

ALARM DATE

ALARM HOURS

ALARM MINUTES

ALARM SECONDS

UNUSED

FLAGS

00-99

01-12

01-31

01-07

00-23

00-59

00-59

01-31

00-23

00-59

00-59

X = Unused, read/writable under Write and Read

bit control

FT = Frequency Test bit

OSC = Oscillator start/stop bit

W = Write bit

R = Read bit

WDS = Watchdog Steering bit

BMB0-BMB4 = Watchdog Multiplier bits

RB0-RB1 = Watchdog Resolution bits

AE = Alarm Flag Enable

Y = Unused, read/writable without Write and

bit control

ABE = Alarm in battery Back-up mode enable

AM1-AM4 = Alarm Mask bits

WF = Watchdog Flag

AF = Alarm Flag

0 = “0” and are read only

BLF = Battery Low Flag

CLOCK OSCILLATOR CONTROL

The Clock oscillator may be stopped at any time. To increase the shelf life of the backup lithium battery

source, the oscillator can be turned off to minimize current drain from the battery. The OSC bit is the

MSB of the seconds register (B7 of 1FF9h). Setting it to a 1 stops the oscillator, setting to a 0 starts the

oscillator. The DS1543 is shipped from Dallas Semiconductor with the clock oscillator turned off, OSC

bit set to a 1.

READING THE CLOCK

When reading the RTC data, it is recommended to halt updates to the external set of double-buffered RTC

registers. This puts the external registers into a static state allowing data to be read without register

values changing during the read process. Normal updates to the internal registers continue while in this

state. External updates are halted when a 1 is written into the read bit, B6 of the Control register (1FF8h).

As long as a 1 remains in the Control register read bit, updating is halted. After a halt is issued, the

registers reflect the RTC count (day, date, and time) that was current at the moment the halt command

was issued. Normal updates to the external set of registers will resume within 1 second after the read bit

is set to a 0.

5 of 17

5 Page

READ CYCLE, AC CHARACTERISTICS

70 ns access

PARAMETER

SYMBOL MIN MAX

Read Cycle Time

tRC 70

Address Access Time

tAA 70

CE to DQ Low-Z

tCEL 5

CE Access Time

tCEA

70

CE Data Off time

tCEZ 25

OE to DQ Low-Z

tOEL

5

OE Access Time

tOEA

35

OE Data Off Time

tOEZ 25

Output Hold from Address

tOH 5

DS1543

(VCC = 5.0V ±10%)

100 ns access

MIN MAX UNITS NOTES

100 ns

100 ns

5 ns

100 ns

35 ns

5 ns

55 ns

35 ns

5 ns

READ CYCLE, AC CHARACTERISTICS

120 ns access

PARAMETER

SYMBOL MIN MAX

Read Cycle Time

tRC 120

Address Access Time

tAA 120

CE to DQ Low-Z

tCEL 5

CE Access Time

tCEA 120

CE Data Off time

tCEZ 40

OE to DQ Low-Z

tOEL

5

OE Access Time

tOEA 100

OE Data Off Time

tOEZ 35

Output Hold from Address

tOH 5

(VCC = 3.3V ±10%)

150 ns access

MIN MAX UNITS NOTES

150 ns 5

150 ns

5

5 ns 5

150 ns

5

50 ns

5

5 ns 5

130 ns

5

35 ns

5

5 ns 5

11 of 17

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet DS1543.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS1543 | 64k NV Timekeeping RAM | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |