|

|

PDF AD1819A Data sheet ( Hoja de datos )

| Número de pieza | AD1819A | |

| Descripción | AC97 SoundPort Codec | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD1819A (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

a

AC ’97 SoundPort® Codec

AD1819A

AC '97 FEATURES

ENHANCED FEATURES

Fully Compliant AC ’97 Analog I/O Component

Support for Multiple Codec Communications

48-Terminal TQFP Package

DSP 16-Bit Serial Port Format

Multibit ⌺⌬ Converter Architecture for Improved

Variable 7 kHz to 48 kHz Sampling Rate with 1 Hz

S/N Ratio >90 dB

Resolution

16-Bit Stereo Full-Duplex Codec

Supports Modem Sample Rates and Filtering

Four Analog Line-Level Stereo Inputs for Connection

Phat™ Stereo 3D Stereo Enhancement

from LINE, CD, VIDEO and AUX

Two Analog Line-Level Mono Inputs for Speakerphone

and PC BEEP

Mono MIC Input Switchable from Two External

Sources

High Quality CD Input with Ground Sense

OStereo Line Level Output

Mono Output for Speakerphone

BPower Management Support

VHDL and Verilog Models of Serial Port Available

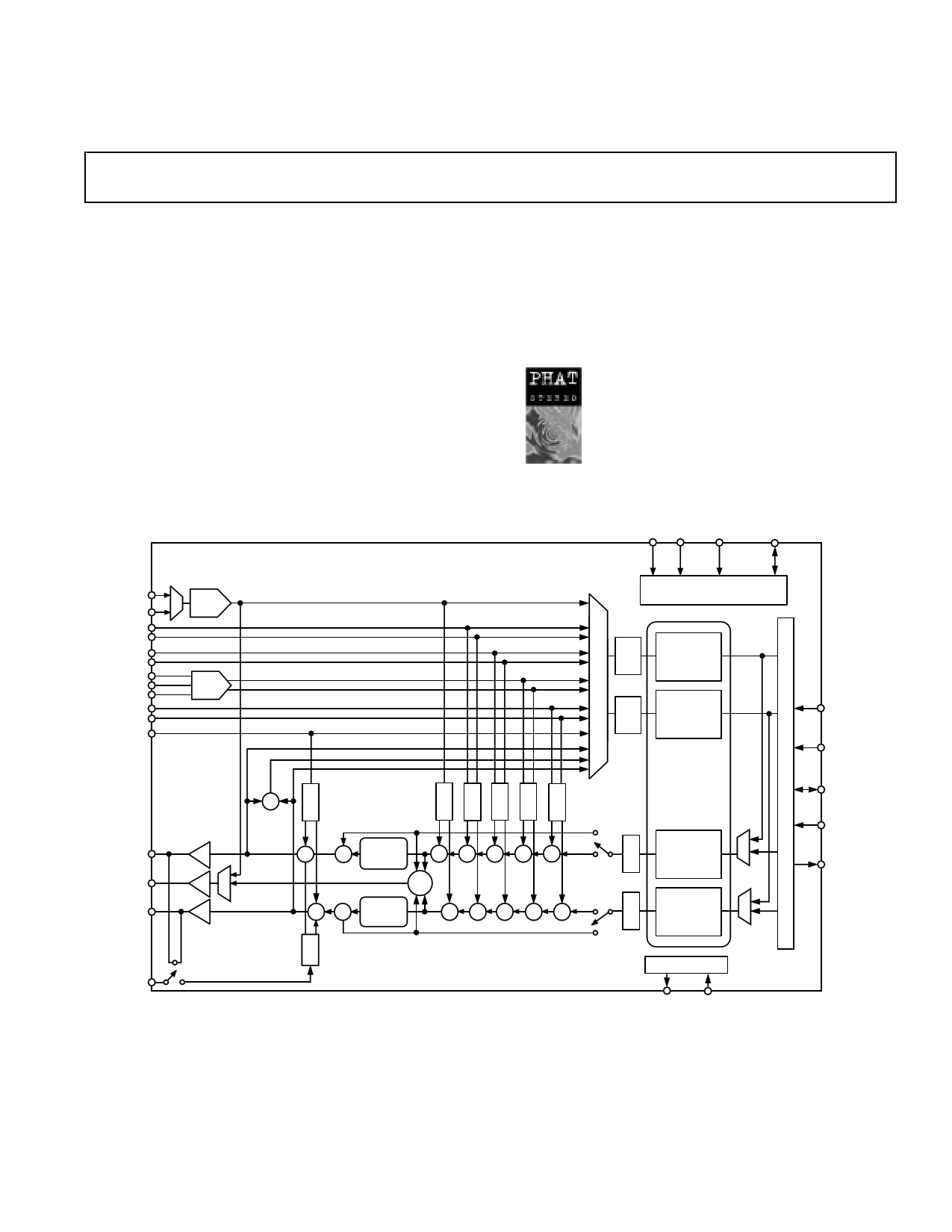

FUNCTIONAL BLOCK DIAGRAM

S CS0 CS1 CHAIN_IN CHAIN_CLK

OLEMIC1

MIC2

TELINE_IN

AD1819A

0dB/

20dB

MASTER/SLAVE

SYNCHRONIZER

AUX

PGA

16-BIT

⌺⌬ A/D

CONVERTER

CD

VIDEO

PHONE_IN

PGA

16-BIT

⌺⌬ A/D

CONVERTER

RESET

SYNC

LINE_OUT_L

MONO_OUT

LINE_OUT_R

MV

MV

MV

PC_BEEP

G

⌺A

M

G GG G G

A AA A A

M MM M M

⌺

⌺

PHAT

STEREO

⌺⌺⌺⌺ ⌺

⌺

⌺

⌺

PHAT

STEREO

⌺ ⌺⌺ ⌺ ⌺

A G = GAIN

M A = ATTENUATE

M = MUTE

MV = MASTER VOLUME

SAMPLE

RATE

GENERATORS

G 16-BIT

A ⌺⌬ D/A

M CONVERTER

G 16-BIT

A ⌺⌬ D/A

M CONVERTER

OSCILLATORS

XTALO XTALI

BIT_CLK

SDATA_OUT

SDATA_IN

SoundPort is a registered trademark of Analog Devices, Inc.

Phat is a trademark of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 1998

1 page

STATIC DIGITAL SPECIFICATIONS

Parameter

High-Level Input Voltage (VIH): Digital Inputs

Low-Level Input Voltage (VIL)

High-Level Output Voltage (VOH), IOH = 2 mA

Low-Level Output Voltage (VOL), IOL = 2 mA

Input Leakage Current

Output Leakage Current

AD1819A

Min Typ

0.4 × DVDD

0.5 × DVDD

–10

–10

Max

0.2 × DVDD

0.2 × DVDD

10

10

Units

V

V

V

V

µA

µA

POWER SUPPLY

Parameter

Min Typ Max

Units

Power Supply Range—Analog

Power Supply Range—Digital

Power Supply Current

Power Dissipation

Analog Supply Current

Digital Supply Current

OPower Supply Rejection (100 mV p-p Signal @ 1 kHz)*

(At Both Analog and Digital Supply Pins, Both ADCs and DACs)

BSCLOCK SPECIFICATIONS*

OParameter

Input Clock Frequency

LRecommended Clock Duty Cycle

ETEPOWER-DOWN STATES

4.5 5.5

4.5 5.5

120

600

60

60

–40

Min Typ Max

24.576

40 50 60

V

V

mA

mW

mA

mA

dB

Units

MHz

%

Parameter

Set Bits

Min Typ Max

Units

ADCs and Input Mux Power-Down

DACs Power-Down

Analog Mixer Power-Down (VREF and VREFOUT On)

Analog Mixer Power-Down (VREF and VREFOUT Off)

Digital Interface Power-Down*

Internal Clocks Disabled*

ADC and DAC Power-Down

VREF Standby Mode*

Total Power-Down

RESET (Low)

PR0

PR1

PR1, PR2

PR0, PR1, PR3

PR4

PR0, PR1, PR4, PR5

PR0, PR1

PR0, PR1, PR2, PR4, PR5

PR0, PR1, PR2, PR3,

PR4, PR5

110

100

54

47

120

85

85

55

220

250

mA

mA

mA

mA

mA

mA

mA

mA

µA

µA

*Guaranteed, not tested.

Specifications subject to change without notice.

REV. 0

–5–

5 Page

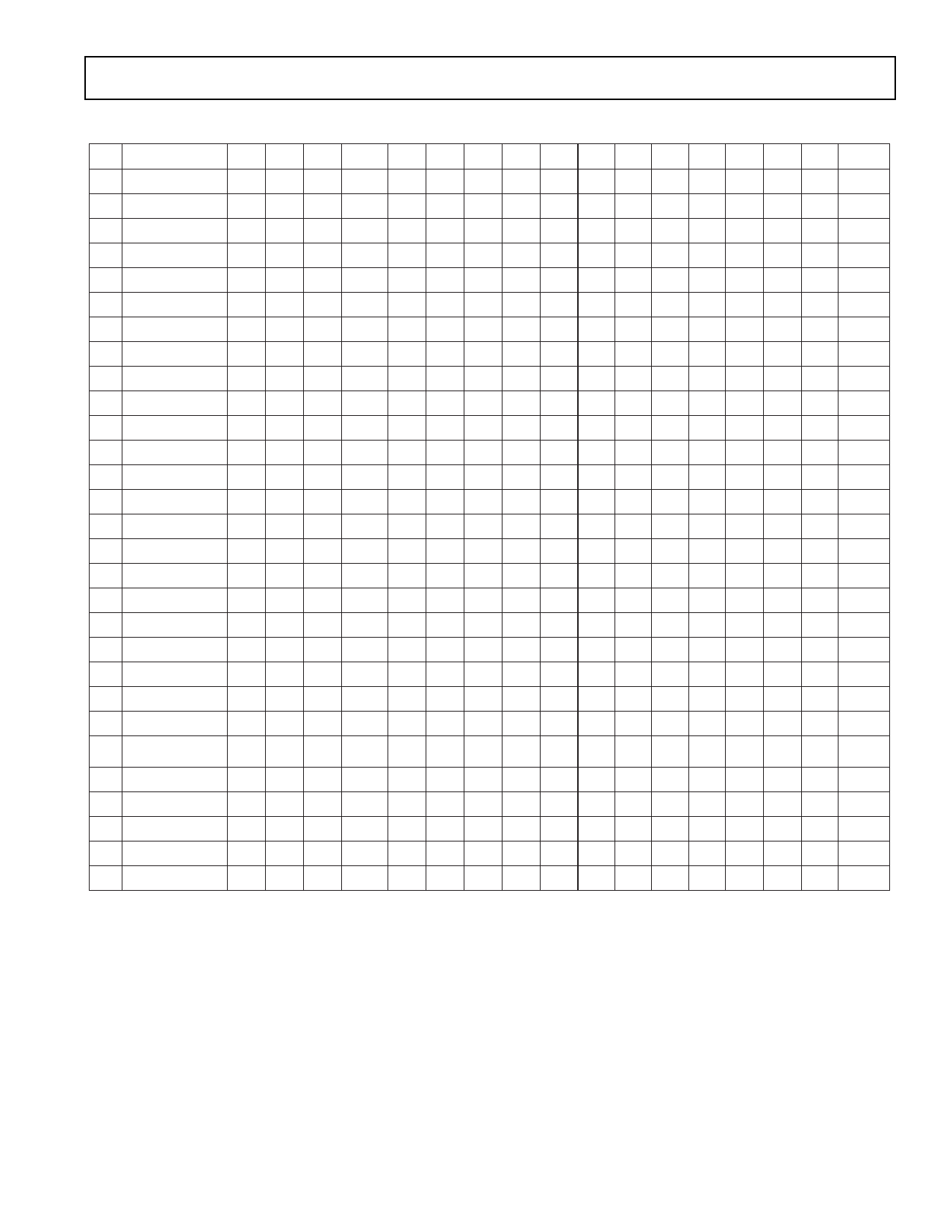

AD1819A

Indexed Control Registers

Reg

Num

Name

00h Reset

D15 D14 D13

D12

D11 D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0 Default

X

SE4 SE3

SE2

SE1 SE0 ID9 ID8 ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

0400h

02h Master Volume

MM

X LMV5 LMV4 LMV3 LMV2 LMV1 LMV0 X

X RMV5 RMV4 RMV3 RMV2 RMV1 RMV0 8000h

04h Reserved

X X X X X X X X XXXXXX XX

X

06h Master Volume Mono

MMM X

X

X

X X X X X X MMV5 MMV4 MMV2 MMV2 MMV1 MMV0 8000h

08h Reserved

X X X X X X X X XXXXXX XX

X

0Ah PC Beep Volume

PCM

X

X

X

X

X

X

X

X

X

X PCV3 PCV2 PCV1 PCV0 X

8000h

0Ch Phone Volume

PHM

X

X

X

X X X X X X X PHV4 PHV3 PHV2 PHV1 PHV0 8008h

0Eh Mic Volume

10h Line In Volume

12h CD Volume

14h Video Volume

O16h Aux Volume

18h PCM Out Vol

B1Ah Record Select

S1Ch Record Gain

O1Eh Reserved

L20h General Purpose

E22h 3D Control

TE24h Reserved

MCM

LM

CVM

VM

AM

OM

X

IM

X

POP

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X X X X X X X M20 X MCV4 MCV3 MCV2 MCV1 MCV0 8008h

X

LLV4 LLV3 LLV2 LLV1 LLV0

X

X

X RLV4 RLV3 RLV2 RLV1 RLV0 8808h

X

LCV4 LCV3 LCV2 LCV1 LCV0

X

X

X RCV4 RCV3 RCV2 RCV1 RCV0 8808h

X

LVV4 LVV3 LVV2 LVV1 LVV0

X

X

X RVV4 RVV3 RVV2 RVV1 RVV0 8808h

X

LAV4 LAV3 LAV2 LAV1 LAV0

X

X

X RAV4 RAV3 RAV2 RAV1 RAV0 8808h

X

LOV4 LOV3 LOV2 LOV1 LOV0

X

X

X ROV4 ROV3 ROV2 ROV1 ROV0 8808h

X X X LS2 LS1 LS0 X X X X X RS2 RS1 RS0 0000h

X

X

LIM3 LIM2 LIM1 LIM0

X

X

X

X RIM3 RIM2 RIM1 RIM0 8000h

X X X X X X XXXXXX XX

X

3D X

X X MIX MS LPBK X X X X X X X 0000h

X X X X X X X X X X DP3 DP2 DP1 DP0 0000h

X X X X X X XXXXXX XX

X

26h Power-Down Contr/Stat

X

X PR5 PR4 PR3 PR2 PR1 PR0 X

X

X

X

REF ANL DAC ADC

0000h

28h Reserved

X X X X X X X X XXXXXX XX

X

72h Reserved

74h Serial Configuration

76h Misc Control Bits

78h Sample Rate 0

X X X X X X X X XXXXXX XX

X

SLOT REGM REGM

16 2

1

DACZ X

X

SR015 SR014 SR013

REGM

0

X

SR012

DRQE

N

X

DLRQ

2

DLSR

DLRQ

1

X

DLRQ

0

ALSR

X

MOD

EN

SR011 SR010 SR09 SR08 SR07

X

SRX1

0D7

SR06

X

SRX8

D7

SR05

X

X

SR04

X

X

SR03

DRRQ DRRQ DRRQ

210

DRSR X ARSR

SR02 SR01 SR00

7000h

0000h

BB80h

7Ah Sample Rate 1

SR115 SR114 SR113 SR112 SR111 SR110 SR19 SR18 SR17 SR16 SR15 SR14 SR13 SR12 SR11 SR10 BB80h

7Ch Vendor ID1

F7 F6 F5 F4 F3 F2 F1 F0 S7 S6 S5 S4 S3 S2 S1 S0 4144h

7Eh Vendor ID2

T7 T6 T5 T4 T3 T2 T1 T0 REV7 REV6 REV5 REV4 REV3 REV2 REV1 REV0 5303h

NOTES

1. All registers not shown and bits containing an X are reserved.

2. Odd register addresses are aliased to the next lower even address.

3. Reserved registers should not be written.

4. Zeros should be written to reserved bits.

REV. 0

–11–

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet AD1819A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD1819A | AC97 SoundPort Codec | Analog Devices |

| AD1819B | AC97 SoundPort Codec | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |